# FUNDAMENTALS OF ELECTRONICS ENGINEERING LABORATORY MANUAL

**B.TECH SEMESTER -I & II**

Subject Code [BEC151/BEC251]

Session: 2022-23, Even Semester

| Name:          |  |

|----------------|--|

| Roll. No.:     |  |

| Group /Branch: |  |

DRONACHARYA GROUP OF INSTITUTIONS

DEPARTMENT OF EEE

#27 KNOWLEDGE PARK 3

GREATER NOIDA

AFFILATED TO Dr. ABDUL KALAM TECHNICAL UNIVERSITY, LUCKNOW

## **Table of Contents**

- 1. Vision and Mission of the Institute

- 2. Vision and Mission of the Department

- 3. Programme Educational Objectives (PEOs)

- 4. Programme Outcomes (POs)

- 5. Programme Specific Outcomes (PSOs)

- 6. University Syllabus

- 7. Course Outcomes (COs)

- 8. CO- PO and CO-PSO mapping

- 9. Course Overview

- 10. List of Experiments

- 11. DOs and DON'Ts

- 12. General Safety Precautions

- 13. Guidelines for students for report preparation

- 14. Lab assessment criteria

- 15. Details of Conducted Experiments

- 16. Lab Experiments

# Vision and Mission of the Institute

#### Vision:

"Dronacharya Group of Institutions, Greater Noida aims to become an Institution of excellence in imparting quality Outcome Based Education that empowers the young generation with Knowledge, Skills, Research, Aptitude and Ethical values to solve Contemporary Challenging Problems"

#### Mission:

- M1: To prepare students for full and ethical participation in a diverse society and encourage lifelong learning by following the principle of 'Shiksha evam Sahayata' i.e. Education and Help.

- **M2:** To impart high-quality education, knowledge and technology through rigorous academic programs, cutting-edge research, and industry collaborations, with a focus on producing engineers and managers who are socially responsible, globally aware, and equipped to address complex challenges.

- M3: Educate students in the best practices of the field as well as integrate the latest research into the academics.

- **M4:** Provide quality learning experiences through effective classroom practices, innovative teaching practices, and opportunities for meaningful interactions between students and faculty.

- **M5:** To devise and implement programmes of education in technology and management that are relevant to the changing needs of society, in terms of breadth of diversity and depth of specialization.

# Vision and Mission of the Department

#### Vision:

- **V1**: To be recognized as a department of excellence to produce competent and ethical students with a worldwide competency and shape them for industry, research, entrepreneurship and higher academic goals.

- **V2**: The department's goal is to help students find, innovate, create, and produce environmentally friendly and socially responsible technology that fulfills the increasing demands of industry.

#### Mission

- M 1: To impart to students technical and ethical knowledge to help them design, implement and control efficient systems and also comprehend the industry's expanding issues.

- M 2: Make every endeavor to engage with academic groups and industry to provide the framework for collaborative research.

# **Programme Educational Objectives (PEOs)**

- **PEO1:** To provide students with a sound knowledge of mathematical, scientific and engineering fundamentals required to solve real world problems.

- **PEO2:** To develop research oriented analytical ability among students and to prepare them for making technical contribution to the society.

- **PEO3:** To develop in students the ability to apply state-of-the-art tools and techniques for designing software products to meet the needs of Industry with due consideration for environment friendly and sustainable development.

- **PEO4:** To prepare students with effective communication skills, professional ethics and managerial skills.

- **PEO5:** To prepare students with the ability to upgrade their skills and knowledge for life-long learning.

# **Programme Outcomes (POs)**

- **PO1: Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- **PO2: Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- **PO3: Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- **PO4:** Conduct investigations of complex problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- **PO5:** Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- **PO6:** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- **PO7: Environment and sustainability:** Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **PO8: Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of engineering practice.

- **PO 9: Individual and teamwork:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- **PO10: Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- **PO11: Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- **PO12: Life-long learning:** Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# **Program Specific Outcomes (PSOs)**

- **PSO1:** Develop applications in the areas of Electronics and Communication Engineering based on the knowledge of Communication systems, Signal processing, VLSI, Embedded Systems and Robotics.

- **PSO2:** Ability to design, analyse, integrate and synthesize different novel systems to be capable for lifelong learning and advanced industrial research.

- **PSO3:** Be proficient enough to make use of the technical concepts, suitable methods and algorithms for research as well as for the social needs.

# **University Syllabus**

#### Part A

- 1. Study of various types of Active & Passive Components based on their ratings.

- 2. Identification of various types of Printed Circuit Boards (PCB) and soldering Techniques.

- 3. PCB Lab: a. Art work & printing of a simple PCB. b. Etching & drilling of PCB

- 4. Winding shop: Step down transformer winding of less than 5VA.

- 5. Soldering shop: Soldering and disordering of Resistor in PCB. Soldering and disordering of IC in PCB. Soldering and disordering of Capacitor in PCB.

#### Part B

- 1. Study of Lab Equipments and Components: CRO, Multimeter, and Function Generator, Power supply-Active, Passive Components and Bread Board.

- 2. P-N Junction diode: Characteristics of PN Junction diode Static and dynamic resistance measurement from graph.

- 3. Applications of PN Junction diode: Half & Full wave rectifier- Measurement of Vrms, Vdc, and ripple factor.

- 4. Characteristics of Zener diode: V-I characteristics of zener diode, Graphical measurement of forward and reverse resistance.

- 5. Characteristic of BJT: BJT in CE configuration.

- 6. To study Operational Amplifier as Adder and Subtractor

- 7. Verification of Truth Table of Various Logic Gate.

- 8. Implementation of the given Boolean function using logic gates in both SOP and POS forms.

# Experiments available on virtual lab

| P-N Junction on diode: Characteristics of  | http://vlabs.iitkgp.ernet.in/be/exp5/index.html      |

|--------------------------------------------|------------------------------------------------------|

| Junction diode - Static and dynamic        |                                                      |

| resistance measurement from graph.         |                                                      |

| A 1' C CDN I C 1' 1 II ICO                 |                                                      |

|                                            | http://vlabs.iitkgp.ernet.in/be/exp6/index.html      |

|                                            | http://vlabs.iitkgp.ernet.in/be/exp7/index.html      |

| Vdc,and ripple factor.                     |                                                      |

| Characteristics of Zener diode: V-I        | http://vlabs.iitkgp.ernet.in/be/exp10/index.html     |

| characteristics of Zener diode, Graphical  |                                                      |

| measurement of forward and reverse         |                                                      |

| resistance.                                |                                                      |

| Characteristic of BJT: BJT in CE           | http://vlabs.iitkgp.ernet.in/be/exp11/index.html     |

| configuration.                             |                                                      |

| To study Operational Amplifier as Adder    | http://vlabs.iitkgp.ernet.in/be/exp17/index.html     |

| and Subtractor                             | http://vlabs.iitkgp.ernet.in/be/exp18/index.html     |

| Verification of Truth Table of Various     | https://de-iitr.vlabs.ac.in/digital-                 |

| Logic Gate.                                | electronicsiitr/exp/truth-table-gates/               |

| Implementation of the given Boolean        | https://de-iitr.vlabs.ac.in/digital-electronicsiitr/ |

| function using logic gates in both SOP and | exp/realization-of-logic-functions/                  |

| POS forms.                                 |                                                      |

# **Course Outcomes (COs)**

Upon successful completion of the course, the students will be able to:

| CO-1 | Demonstrate the behavior of various applications PN junction diode                     |

|------|----------------------------------------------------------------------------------------|

| CO-2 | Conduct experiments illustrating the characteristics of BJT and applications of OPAMP. |

| CO-3 | Implementation and truth table verification of various logic gates.                    |

# **CO-PO Mapping**

|                                  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| CO1                              | 2   | 3   | 2   | 3   | 3   | 2   | 3   | 2   | 1   | 2    | 3    | 2    |

| CO2                              | 1   | 2   | 3   | 2   | 2   | 2   | 2   | 3   | 1   | 3    | 2    | 2    |

| CO3                              | 2   | 3   | 2   | 3   | 3   | 3   | 3   | 2   | 2   | 3    | 2    | 2    |

| Course<br>Correlation<br>mapping | 2   | 3   | 2   | 3   | 3   | 2   | 3   | 2   | 1   | 3    | 2    | 2    |

Correlation Levels: High-3, Medium-2, Low-1

# **CO-PSO** Mapping

|                                  | PSO1 | PSO2 | PSO3 |

|----------------------------------|------|------|------|

| CO1                              | 2    | 3    | 2    |

| CO2                              | 2    | 3    | 2    |

| CO3                              | 2    | 3    | 2    |

| Course<br>Correlation<br>mapping | 2    | 3    | 2    |

# **Course Overview**

In this lab students will study about the basics of different kinds of diodes like PN junction diode, zener diode, clipper and clampers etc. Additionally, BJT and FET along with its various configurations. Study of Half wave and full wave rectifiers using with or without filters. Measurement of Op-Amp parameters: Common mode gain, differential mode gain, CMRR, slew rate. Applications of Op-Amp: Op-Amp as summing amplifier, difference amplifier, integrator and differentiator. Field effect transistors: Single stage common source FET amplifier –plot of gain in dB Vs frequency. Verification of truth tables using different gates. At last, Simulation of different circuits studied in the lab using any available simulation software's.

# **List of Experiments mapped with COs**

| S. No | Aim of the                                                       | COs |  |  |

|-------|------------------------------------------------------------------|-----|--|--|

| 1.    | Study of CRO Operations and its Applications                     | CO1 |  |  |

| 2.    | P-N Junction Diode Characteristics                               | CO1 |  |  |

| 3.    | Zener Diode Characteristics                                      | CO1 |  |  |

| 4.    | Half Wave Rectifier With & Without Filter                        | CO1 |  |  |

| 5.    | Full Wave Rectifier With & Without Filter                        | CO1 |  |  |

| 6.    | BJT Characteristics (CE Configuration)                           |     |  |  |

| 7.    | BJT Characteristics (CB Configuration)                           |     |  |  |

| 8.    | FET Characteristics                                              | CO2 |  |  |

| 9.    | LED Characteristics                                              | CO1 |  |  |

| 10.   | Input & Output Characteristics of Transistor in CB Configuration | CO2 |  |  |

| 11.   | Input & Output Characteristics of Transistor in CE Configuration | CO2 |  |  |

| 12.   | Applications of Op-Amp (Inverting and Non – Inverting Amplifier) | CO2 |  |  |

| 13.   | Verification of Truth Tables for Different Logic Gates           | CO3 |  |  |

### **DOs and DON'Ts**

- 1. Treat every electrical device like it is energized, even if it does not look like it is plugged in or operational.

- 2. Unplug appliances before performing any service or repairs on them.

- 3. When working on electrical devices, only use tools that have official "non-conducting" handles.

- 4. Try to limit the use of electrical equipment in rooms that are very cold or have a lot of condensation.

- 5. When handling electrical equipment, make sure your hands are dry.

- 6. If you spill any kind of liquid on electrical equipment, first immediately shut off power to the equipment via the main switch or circuit breaker and then unplug the equipment itself.

- 7. Keep all electrical circuit contact points enclosed.

#### DON'Ts

- 1. First and foremost don't touch active electrical circuits.

- 2. Never touch electrical equipment when any part of your body is wet, (that includes fair amounts of perspiration).

- 3. Do not store liquids of any sort near electrical equipment.

- 4. If a person comes into contact with an energized electrical conductor, do not touch the equipment, its cords, or the person affected because the charge may pass to you. Instead, shut down the main power source via the circuit breaker and then unplug the equipment using a leather belt.

- 5. Do not wear metal of any sort if you are working on electrical equipment.

- 6. Also, do not try to poke, probe, or fix electrical equipment with objects like pencils or rulers because the metal in them can serve as a form of conductor.

# **General Safety Precautions**

### **Precautions (In case of Injury or Electric Shock)**

- 1. To break the victim with live electric source, use an insulator such as firewood or plastic to break the contact. Do not touch the victim with bare hands to avoid the risk of electrifying yourself.

- 2. Unplug the risk of faulty equipment. If the main circuit breaker is accessible, turn the circuit off.

- If the victim is unconscious, start resuscitation immediately, use your hands to press the

chest in and out to continue breathing function. Use mouth-to-mouth resuscitation if

necessary.

### **Precautions (In case of Fire)**

- 1. Turn the equipment off. If the power switch is not immediately accessible, take plug off.

- 2. If fire continues, try to curb the fire if possible, by using the fire extinguisher or by covering it with a heavy cloth if possible isolate the burning equipment from the other surrounding equipment.

- 3. Sound the fire alarm by activating the nearest alarm switch located in the hallway.

- 4. Call security and emergency department immediately:

Emergency: 201 (Reception) Security: 231 (Gate No.1)

# **Guidelines to Students for Report Preparation**

All students are required to maintain a record of the experiments conducted by them. Guidelines for its preparation are as follows:-

- 1) All files must contain a title page followed by an index page. The files will not be signed by the faculty without an entry in the index page.

- 2) Student's Name, Roll number and date of conduction of experiment must be written on all pages.

- 3) For each experiment, the record must contain the following

- (i) Aim/Objective of the experiment

- (ii) Pre-experiment work (as given by the faculty)

- (iii) Lab assignment questions and their solutions

- (iv) Test Cases (if applicable to the course)

- (v) Results/output

#### Note:

- 1. Students must bring their lab record along with them whenever they come for the lab.

- 2. Students must ensure that their lab record is regularly evaluated.

# **Lab Assessment Criteria**

An estimated 10 lab classes are conducted in a semester for each lab course. These lab classes are assessed continuously. Each lab experiment is evaluated based on 5 assessment criteria as shown in following table. Assessed performance in each experiment is used to compute Course Outcomes attainment as well as internal marks in the lab course.

| attainment as well                                              | l as internal marks in the                                                                                                                                                                  | e lab course.                                                                                                    |                                                                                                                                                                                                                                                              |                                                                                     |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Grading                                                         | Exemplary (4)                                                                                                                                                                               | Competent (3)                                                                                                    | Needs                                                                                                                                                                                                                                                        | Poor (1)                                                                            |

| Criteria                                                        |                                                                                                                                                                                             |                                                                                                                  | Improvement (2)                                                                                                                                                                                                                                              |                                                                                     |

| AC1: Designing experiments                                      | The student chooses the problems to explore.                                                                                                                                                | The student chooses<br>the problems but<br>does not set an<br>appropriate goal as<br>how to explore.             | Student fails to define the problem adequately                                                                                                                                                                                                               | Student does<br>not identify the<br>problem                                         |

| AC2: Collecting data through observation and/or experimentation | Develops a clear procedure for investigating the problem                                                                                                                                    | Observations are completed with necessary theoretical calculations proper identification of required components. | Observations are completed with necessary theoretical calculations but without proper understanding. Obtain the correct values for only few components after calculations. Followed the given experimental procedures, but obtained results with some errors | Observations are incomplete. Lacks the appropriate knowledge of the lab procedures. |

| AC3: Interpreting data  AC4: Drawing conclusions                | Decides what data and observations are to be collected and verified  Interprets and analyses the data in order to propose                                                                   |                                                                                                                  |                                                                                                                                                                                                                                                              | _                                                                                   |

| AC5: Lab record assessment                                      | viable conclusions and solutions  Well-organized and confident presentation of record & able to correlate the theoretical concepts with the concerned lab results with appropriate reasons. | conclusions drawn is not up to the mark  Presentation of record acceptable                                       | any kind of conclusions  Presentation of record lacks clarity and organization                                                                                                                                                                               | conclusions and solutions  No efforts exhibited                                     |

# LAB EXPERIMENTS

### EXPERIMENT NO. -1

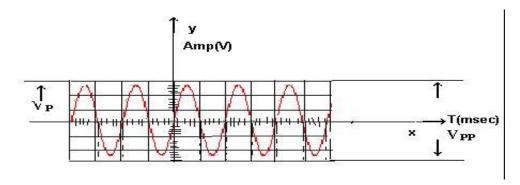

**OBJECTIVE:** To observe front panel control knobs and to find amplitude, time period and frequency for given waveforms.

**APPARATUS REQUIRED:**CRO, Function generator and probes

#### **THEORY:**

C.R.O. (Cathode Ray Oscilloscope) is the instrument which is used to observe signal waveforms. Signals are displayed in time domain i.e. variation in amplitude of the signal with respect to time is plotted on the CRO screen. X-axis represents time and Y-axis represents amplitude. It is used to measure amplitude, frequency and phase of the waveforms. It is also used to observe shape of the waveform. C.R.O. is useful for troubleshooting purpose. It helps us to find out gain of amplifier, test oscillator circuits. We can measure amplitude and frequency of the waveforms at the different test points in our circuit. Thus, it helps us for fault finding procedure. In dual channel C.R.O. X-Y mode is available which is used to create patterns. Latest digital storage oscilloscope display voltage and frequency directly on the LCD and does not require any calculations. It can also store waveform for further analysis. More detailed study on C.R.O. will be covered in EMI laboratory (SEM-V). In this practical, we will measure amplitude and frequency of the different waveforms like sine wave, square wave, triangular wave and ramp wave.

#### **PROCEDURE**

- 1. Understand the significance of each and every knob on the CRO.

- 2. From the given function generator feed in a sinusoidal wave and adjust the time base knob and the amplitude knob to observe the waveform as a function of time.

- 3. Measure the time period and amplitude (peak to peak) of the signal. Find the frequency and verify if the same frequency is given fro the function generator.

- 4. Observe two waveforms simultaneously on the two channels of a CRO.

- 5. Repeat the above steps for pulse and triangular waveforms.

- 6. Report the readings and the waveforms taken.

### **MEASUREMENTS:**

Amplitude = no. of vertical divisions \* Volts/div.

Time period = no. of horizontal divisions \* Time/div. Frequency=(1/T)Hz

#### **MODEL GRAPHS:**

**APPLICATIONS OF CRO:**

- 1. Measurement of current

- 2. Measurement of voltage

- 3. Measurement of power

- 4. Measurement of frequency

- 5. Measurement of phase angle

- 6. To see transistor curves

- 7. To trace and measuring signals of RF, IF and AF in radio and TV.

- 8. To trace visual display of sine waves.

3

# Observation table:

| Function          | Vertical<br>Division<br>(a) | Volt/div<br>(b) | Amplitude<br>(p-p)<br>V=a*b | Horizont<br>al Div<br>(c) | Time/d iv (d) | Time<br>T<br>=c*d | Freq.<br>F=1/T |

|-------------------|-----------------------------|-----------------|-----------------------------|---------------------------|---------------|-------------------|----------------|

| Sine<br>wave      |                             |                 |                             |                           |               |                   |                |

| Square<br>Wave    |                             |                 |                             |                           |               |                   |                |

| Triangula<br>Wave | r                           |                 |                             |                           |               |                   |                |

| Ramp<br>Wave      |                             |                 |                             |                           |               |                   |                |

|                   |                             |                 |                             |                           |               |                   |                |

| Draw ob | Draw observed waveforms: |  |  |  |  |  |  |  |  |

|---------|--------------------------|--|--|--|--|--|--|--|--|

| Sine wa | Sine wave: (Amplitude:)  |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

|         |                          |  |  |  |  |  |  |  |  |

# FUNDAMENTALS OF ELECTRONICS ENGINEERING(BEC151/BEC251)

| Square wave: (Amplitude : |          |          | F        | requenc | y:      |       | ) |   |  |

|---------------------------|----------|----------|----------|---------|---------|-------|---|---|--|

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

| Triang                    | ular wav | ve: (Amp | litude : |         | _ Frequ | ency: |   | ) |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

| Ramp:                     | ((Amplit | tude: _  |          | Frequer | ncy:    |       | ) |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

|                           |          |          |          |         |         |       |   |   |  |

$Result: \ \ \ Thus, \ studied \ the \ whole \ characteristics \ of \ CRO \ and \ plotted \ the \ waveforms$

### **EXPERIMENT 2**

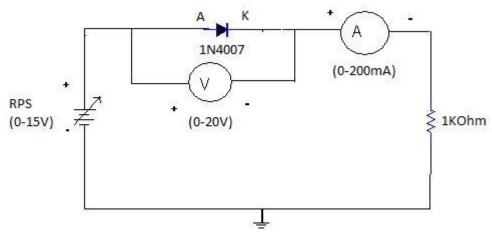

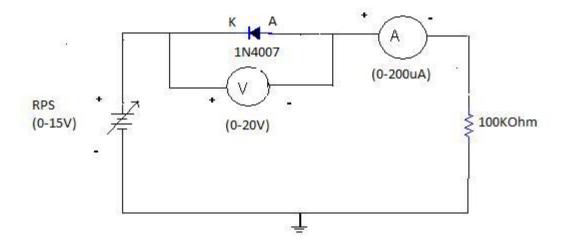

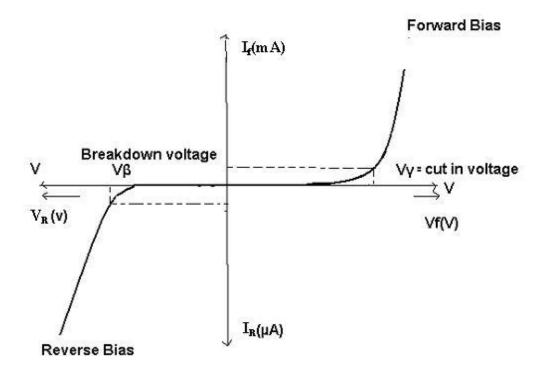

**OBJECTIVE**: To observe and draw the Forward and Reverse bias V-I Characteristics of a P-N Junction diode.

#### **APPARATUS REQUIRED:**

P-N Diode 1N4007

Regulated Power supply (0-15V)

Resistor 1KΩ

Ammeters (0-200mA, 0-200µA)

Voltmeter (0-20V)

Breadboard

Connecting wires

#### THEORY:

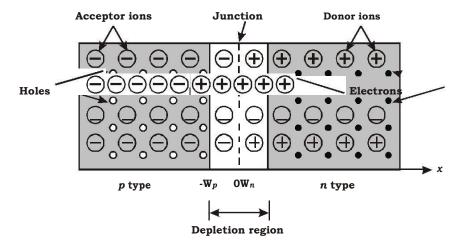

The semiconductor diode is formed by doping P-type impurity in one side and N-type of impurity in another side of the semiconductor crystal forming a p-n junction as shown in the following figure.

At the junction initially free charge carriers from both side recombine forming negatively charged ions in P side of junction(an atom in P-side accept electron and becomes negatively charged ion) and positively charged ion on n side(an atom in n-side accepts hole i.e. donates electron and becomes positively charged ion)region. This region deplete of any type of free charge carrier is called as depletion region. Further recombination of free carrier on both side is prevented because of the depletion voltage generated due to charge carriers kept at distance by depletion (acts as a sort of insulation) layer as shown dotted in the above figure.

#### Working principle:

When voltage is not applied across the diode, depletion region forms as shown in the above figure. When the voltage is applied between the two terminals of the diode (anode and cathode) two possibilities arises depending on polarity of DC supply.

[1] Forward-Bias Condition: When the +Ve terminal of the battery is connected to P-type material & -Ve terminal to N-type terminal as shown in the circuit diagram, the diode is said to be forward biased. The application of forward bias voltage will force electrons in N-type and holes in P-type material to recombine with the ions near boundary and to flow crossing junction. This reduces width of depletion region. This further will result in increase in majority carriers flow across the junction. If forward bias is

further increased in magnitude the depletion region width will continue to decrease, resulting in exponential rise in current as shown in ideal diode characteristic curve.

[2]Reverse-biased: If the negative terminal of battery (DC power supply) is connected with P-type terminal of diode and +Ve terminal of battery connected to N type then diode is said to be reverse biased. In this condition the free charge carriers (i.e. electrons in N-type and holes in P-type) will move away from junction widening depletion region width. The minority carriers (i.e. –ve electrons in p-type and +ve holes in n-type) can cross the depletion region resulting in minority carrier current flow called as reverse saturation current(Is). As no of minority carrier is very small so the magnitude of Is is few microamperes. Ideally current in reverse bias is zero.

In short, current flows through diode in forward bias and does not flow through diode in reverse bias. Diode can pass current only in one direction.

#### **CIRCUIT DIAGRAM:**

#### **FORWARD BIAS:**

## **REVERSE BIAS**:

#### **MODEL GRAPH:**

#### **PROCEDURE:**

#### FORWARD BIAS:

- 1. Connections are made as per the circuit diagram.

- 2. For forward bias, the RPS +ve is connected to the anode of the diode and RPS –ve is connected to the cathode of the diode,

- 3. Switch on the power supply and increases the input voltage (supply voltage) in steps.

- 4. Note down the corresponding current flowing through the diode and voltage across the diode for each and every step of the input voltage.

- 5. The reading of voltage and current are tabulated.

- 6. Graph is plotted between voltage and current.

#### **OBSERVATIONS:**

| S.NO | $V_{f}(V)$ | If (mA) |

|------|------------|---------|

|      |            |         |

|      |            |         |

|      |            |         |

|      |            |         |

#### **PROCEDURE**:

#### **REVERSE BIAS:**

- 7. Connections are made as per the circuit diagram.

- 8. For reverse bias, the RPS +ve are connected to the cathode of the diode and RPS –ve is connected to the anode of the diode.

- 9. Switch on the power supply and increase the input voltage (supply voltage) in steps

- 10. Note down the corresponding current flowing through the diode voltage across the diode for each and every step of the input voltage.

- 11. The readings of voltage and current are tabulated

- 12. Graph is plotted between voltage and current.

#### **OBSEVATIONS:**

| S.NO | $V_{r}(V)$ | I <sub>r</sub> (mA) |

|------|------------|---------------------|

|      |            |                     |

|      |            |                     |

|      |            |                     |

|      |            |                     |

**RESULT:** Forward and Reverse Bias characteristics for a p-n diode is observed

### **EXPERIMENT 3**

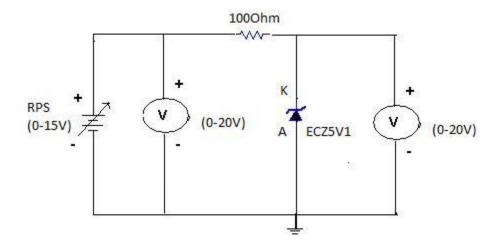

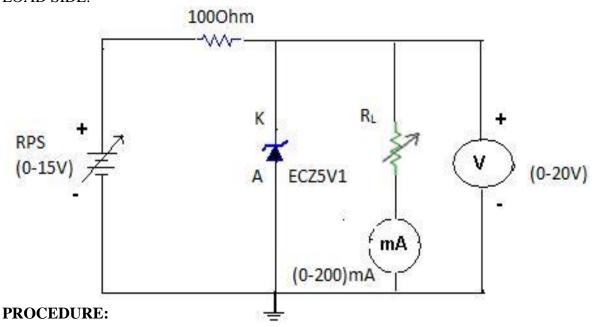

**OBJECTIVE:** To observe and draw the regulator characteristics of a zener diode at supply and load side.

### **APPARATUS REQUIRED:**

Zener diode – ECZ5V1

Regulated Power Supply (0-15V)

Voltmeter (0-20V)

Ammeter (0-200mA)

Resistor (1K $\Omega$ )

Breadboard

Connecting wires

#### THEORY:

A zener diode is heavily doped p-n junction diode, specially made to operate in the break down region. A p-n junction diode normally does not conduct when reverse biased. But if the reverse bias is increased, at a particular voltage it starts conducting heavily. This voltage is called Break down Voltage. High current through the diode can permanently damage the device. To avoid high current, we connect a resistor in series with zener diode. Once the diode starts conducting it maintains almost constant voltage across the terminals whatever may be the current through it, i.e., it has very low dynamic resistance. It is used in voltage regulators.

#### **CIRCUIT DIAGRAM:**

#### SUPPLY SIDE:

#### LOAD SIDE:

#### **SUPPLY SIDE:**

- 9. Connections are made as per the circuit diagram.

- 10. The Regulated power supply voltage is increased in steps.

- 11. For different input voltages  $(V_i)$  corresponding output voltages  $(V_o)$  are observed and then noted in the tabular form.

- 12. A graph is plotted between input voltage  $(V_i)$  and the output voltage  $(V_0)$ .

#### LOAD SIDE:

- 1. Connection are made as per the circuit diagram

- 2. The load is placed in full load condition and the output voltage  $(V_0)$ , load current  $(I_L)$  are measured.

- 3. The above step is repeated by decreasing the value of the load in steps.

- 4. All the readings are tabulated and a graph is plotted between load current ( $I_L$ ) and the output voltage ( $V_o$ ).

#### **OBSERVATIONS:-**

**SUPPLY SIDE:-**

| S.NO | S.NO $V_i(V)$ $V_o(V)$ |  |

|------|------------------------|--|

|      |                        |  |

|      |                        |  |

|      |                        |  |

LOAD SIDE:-

| S.NO | I <sub>L</sub> (V) | V <sub>o</sub> (V) |

|------|--------------------|--------------------|

|      |                    |                    |

|      |                    |                    |

|      |                    |                    |

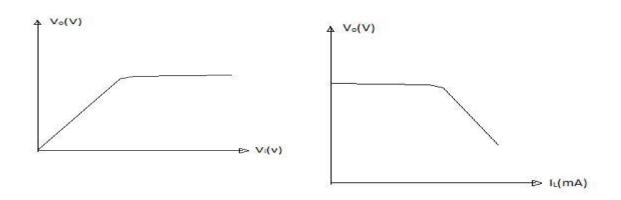

### **MODEL GRAPH:**

SUPPLY SIDE:

LOAD SIDE

**RESULT:** Regulator characteristics of zener diode are obtained and graphs are plotted for load and supply side.

#### **EXPERIMENT 4**

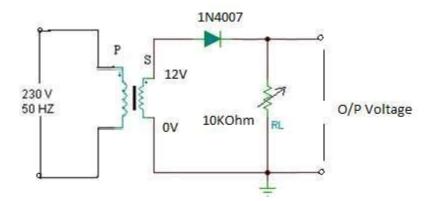

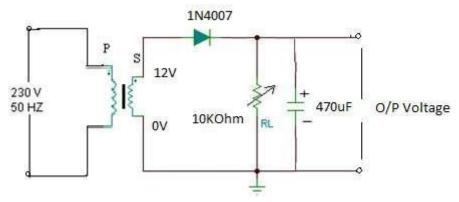

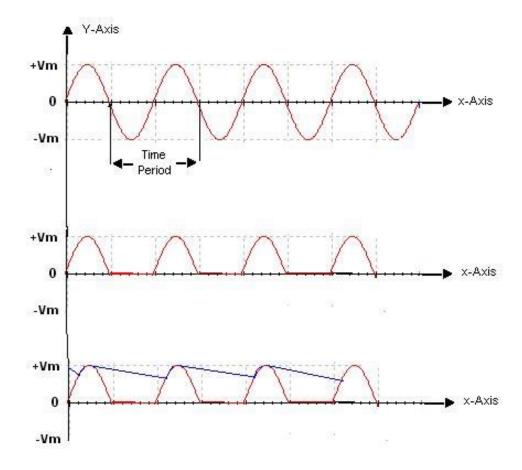

**OBJECTIVE:** To obtain the % regulation and ripple factor of a half wave rectifier with and without filter.

#### **APPARATUS REQUIRED:**

AC Supply 12V

PN Diode, 1N4007

Capacitor, 470µF

Variable Resistor (0-10) K $\Omega$

Connecting wires

Breadboard

Multimeter

#### **THEORY:**

During positive half-cycle of the input voltage, the diode D1 is in forward bias and conducts through the load resistor R1. Hence the current produces an output voltage across the load resistor R1, which has the same shape as the +ve half cycle of the input voltage. During the negative half-cycle of the input voltage, the diode is reverse biased and there is no current through the circuit. i.e., the voltage across R1 is zero.

The net result is that only the +ve half cycle of the input voltage appears across the load. The average value of the half wave rectified o/p voltage is the value measured on dc voltmeter. For practical circuits, transformer coupling is usually provided for two reasons.

- 1. The voltage can be stepped-up or stepped-down, as needed.

- 2. The ac source is electrically isolated from the rectifier. Thus preventing shock hazards in the secondary circuit.

#### **CIRCUIT DIAGRAMS:**

#### WITHOUT FILTER:

#### WITH FILTER:

#### **PROCEDURE:**

- 1. Connections are made as per the circuit diagram.

- 2. Connect the primary side of the transformer to ac mains and the secondary side to the rectifier input.

- 3. By the multimeter, measure the ac input voltage of the rectifier and, ac and dc voltage at the output of the rectifier.

- 4. Find the theoretical of dc voltage by using the formula,

$$V_{dc} = V_m / \pi$$

Where, V<sub>m</sub>=2Vrms, (V<sub>rms</sub>=output ac voltage.)

The Ripple factor is calculated by using the formula r=ac output voltage/dc output voltage.

#### **REGULATION CHARACTERSTICS:**

- 1. Connections are made as per the circuit diagram.

- 2. By increasing the value of the rheostat, the voltage across the load and current flowing through the load are measured.

- 3. The reading is tabulated.

- 4. Draw a graph between load voltage (V  $_L$  and load current (  $I_L$  ) taking V  $_L$  on X-axis and  $I_L$  on y-axis

- 5. From the value of no-load voltages, the % regulation is calculated using the formula,

#### **OBSERVATIONS:**

WITHOUT FILTER:

| R <sub>L</sub> (KΩ) | Vac<br>(Volts) | V <sub>dc</sub><br>(Volts) | Ripple Factor = V <sub>ac</sub> / V <sub>dc</sub> | % Regulation<br>(V <sub>NL</sub> -V <sub>FL</sub> )/V <sub>FL</sub> *100 |

|---------------------|----------------|----------------------------|---------------------------------------------------|--------------------------------------------------------------------------|

|                     |                |                            |                                                   |                                                                          |

|                     |                |                            |                                                   |                                                                          |

|                     |                |                            |                                                   |                                                                          |

#### WITH FILTER:

| RL   | Vac     | $V_{dc}$ | Ripple Factor     | % Regulation                                             |

|------|---------|----------|-------------------|----------------------------------------------------------|

| (ΚΩ) | (Volts) | (Volts)  | $= V_{ac}/V_{dc}$ | (V <sub>NL</sub> -V <sub>FL</sub> )/V <sub>FL</sub> *100 |

|      |         |          |                   |                                                          |

|      |         |          |                   |                                                          |

|      |         |          |                   |                                                          |

|      |         |          |                   |                                                          |

|      |         |          |                   |                                                          |

#### **MODEL GRAPHS:**

HALFWAVE RECTIFIER (WITH & WITHOUT FILTER):

**RESULT:** The Ripple factor and % regulation for the Half-wave Rectifier with and without filters is measured.

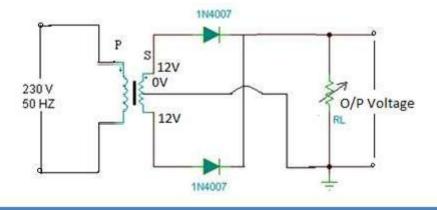

#### **EXPERIMENT 5**

**OBJECTIVE:** To find the Ripple factor and regulation of a Full-wave Rectifier with and without filter.

#### **APPARATUS REQUIRED:**

AC Supply (12V-0-12V)

PN Diodes 1N4007

Capacitor 470µF

**Connecting Wires**

Variable resistor (0-10)  $K\Omega$

Breadboard

Multimeter

#### THEORY:

The circuit of a center-tapped full wave rectifier uses two diodes D1&D2. During positive half cycle of secondary voltage (input voltage), the diode D1 is forward biased and D2 reverse biased. The diode D1 conducts and current flows through load resistor R<sub>L</sub>. During negative half cycle, diode D2 becomes forward biased and D1 reverse biased. Now, D2 conducts and current flows through the load resistor R<sub>L</sub> in the same direction. There is a continuous current flow through the load resistor R<sub>L</sub>, during both the half cycles and will get unidirectional current as show in the model graph. The difference between full wave and half wave rectification is that a full wave rectifier allows unidirectional (one way) current to the load during the entire 360 degrees of the input signal and half-wave rectifier allows this only during one half cycle (180 degree).

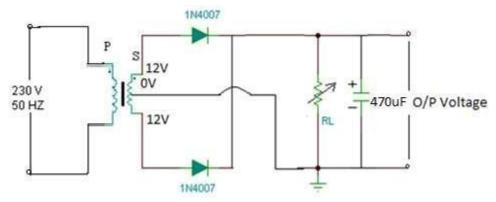

#### **CIRCUIT DIAGRAM:**

#### WITHOUT FILTER:

#### WITH FILTER:

#### **PROCEDURE:**

- 1. Connections are made as per the circuit diagram.

- 2. Connect the ac mains to the primary side of the transformer and the secondary side to the rectifier.

- 3. Measure the ac voltage at the input side of the rectifier.

- 4. Measure both ac and dc voltages at the output side the rectifier.

- 5. Find the theoretical value of the dc voltage by using the formula  $V_{dc}$ =2 $V_m/\pi$

- 6. Connect the filter capacitor across the load resistor and measure the values of  $V_{ac}$  and  $V_{dc}$  at the output.

- 7. The theoretical values of Ripple factors with and without capacitor are calculated.

- 8. From the values of  $V_{ac}$  and  $V_{dc}$  practical values of Ripple factors are calculated. The practical values are compared with theoretical values.

### **OBSERVATIONS:**

#### WITHOUT FILTER:

| R <sub>L</sub> (Ohms) | Vac<br>(Volts) | V <sub>dc</sub><br>(Volts) | Ripple Factor = V <sub>ac</sub> / V <sub>dc</sub> | % Regulation<br>(V <sub>NL</sub> -V <sub>FL</sub> )/V <sub>FL</sub> *100 |

|-----------------------|----------------|----------------------------|---------------------------------------------------|--------------------------------------------------------------------------|

|                       |                |                            |                                                   |                                                                          |

|                       |                |                            |                                                   |                                                                          |

#### WITH FILTER:

| $V_{ac}$ | $V_{dc}$ | Ripple Factor     | % Regulation                                             |

|----------|----------|-------------------|----------------------------------------------------------|

| (Volts)  | (Volts)  | $= V_{ac}/V_{dc}$ | (V <sub>NL</sub> -V <sub>FL</sub> )/V <sub>FL</sub> *100 |

|          |          |                   |                                                          |

|          |          |                   |                                                          |

|          |          |                   |                                                          |

|          |          |                   |                                                          |

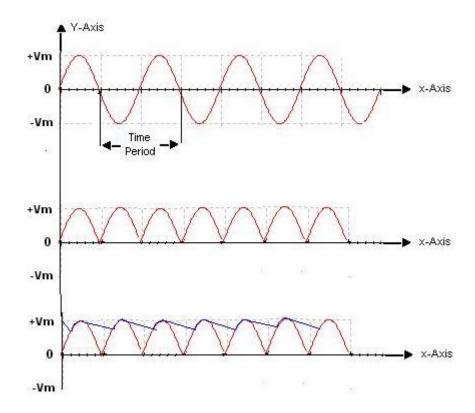

### **MODEL GRAPHS:**

FULLWAVE RECTIFIER (WITH & WITHOUT FILTER):

#### **RESULT**:

The ripple factor of the Full-wave rectifier (with filter and without filter) is calculated.

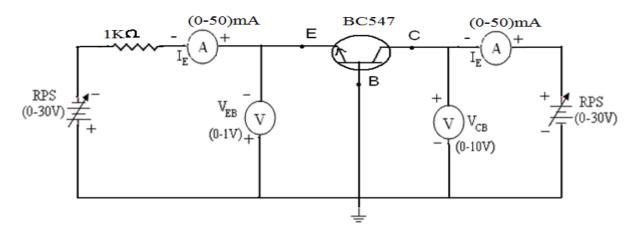

**OBJECTIVE:** 1.To observe and draw the input and output characteristics of a transistor connected in common base configuration.

2. To find  $\alpha$  of the given transistor.

#### **APPARATUS REQUIRED:**

| NAME OF THE EQUIPMENT  | RANGE             | QUANTITY |

|------------------------|-------------------|----------|

| Transistor             | BC 547            |          |

| Regulated power supply | (0-30)V           |          |

| Voltmeter              | (0-20V),(0-2)V    |          |

| Ammeters               | (0-50)mA,(0-50)mA |          |

| Resistor               | 1ΚΩ               |          |

| Bread board            |                   |          |

| Connecting wires       |                   |          |

**THEORY:** A transistor is a three terminal active device. The terminals are emitter, base, collector. In CB configuration, the base is common to both input (emitter) and output (collector). For normal operation, the E-B junction is forward biased and C-B junction is reverse biased. With an increasing the reverse collector voltage, the space-charge width at the output junction increases and the effective base width 'W' decreases. This phenomenon is known as "Early effect". Then, there will be less chance for recombination within the base region. With increase of charge gradient with in the base region, the current of minority carriers injected across the emitter junction increases. The current amplification factor of CB configuration is given by  $\alpha = \Delta I_{\rm C}/\Delta I_{\rm E}$

#### **PROCEDURE:**

## **INPUT CHARACTERISTICS:**

- 1. Connections are made as per the circuit diagram.

- 2. For plotting the input characteristics, the output voltage  $V_{CB}$  is kept constant at 0V and for different values of  $V_{EB}$  note down the values of  $I_E$ .

- 3. Repeat the above step keeping  $V_{CB}$  at V, V, and V. All the readings are tabulated.

- 4. A graph is drawn between  $V_{EB}$  and  $I_{E}$  for constant  $V_{CB}$ .

#### **OUTPUT CHARACTERISTICS:**

- 1. Connections are made as per the circuit diagram.

- 2. For plotting the output characteristics, the input  $I_E$  iskept constant at 5m A and for different values of  $V_{CB}$ , note down the values of  $I_C$ .

- 3. Repeat the above step for the values of  $I_E$  at mA, mA, and mA, all the readings are tabulated.

- 4. A graph is drawn between V<sub>CB</sub> and Ic for constant I

## **PRECAUTIONS:**

- 1. The supply voltages should not exceed the rating of the transistor.

- 2. Meters should be connected properly according to their polarities.

#### **CIRCUIT**

#### **DIAGRAM:**

# **OBSERVATIONS:**

# **INPUT CHARACTERISTICS:**

|      | $\mathbf{V}_{\mathrm{CB}}$ | V                   | $V_{CB=}$           | V                   | V <sub>CB</sub> =   | V                   |

|------|----------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| S.No | V <sub>EB</sub> (V)        | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) | V <sub>EB</sub> (V) | I <sub>E</sub> (mA) |

|      |                            |                     |                     |                     |                     |                     |

|      |                            |                     |                     |                     |                     |                     |

|      |                            |                     |                     |                     |                     |                     |

|      |                            |                     |                     |                     |                     |                     |

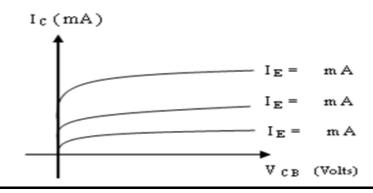

# **OUTPUT CHARACTERISTICS:**

|      | $I_{E=}$            | mA                  | $I_{E=}$            | mA                  | I <sub>E</sub> =    | mA                  |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| S.No | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) | V <sub>CB</sub> (V) | I <sub>C</sub> (mA) |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

# **CALCULATIONS:-**

Input impedance =  $(\Delta V_{EB}V/\Delta I_{E})\Omega$

Output impedance = $(\Delta V_{CB}V/\Delta I_{C})\Omega$

Current gain =  $\Delta I_C / \Delta I_E$

# Input Characteristics:

# Output characteristics:

**RESULT:** Thus studied the input and output characteristics of a transistor connected in common base configuration.

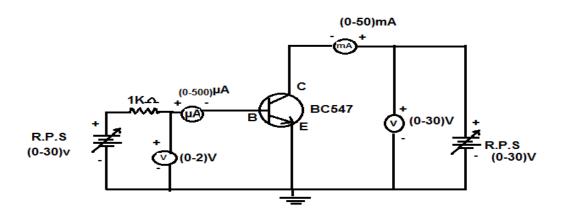

**OBJECTIVE:** 1. To draw the input and output characteristics of transistor connected in

CE configuration

2. To find  $\beta$  of the given transistor

# **APPARATUS REQUIRED**

# **THEORY:**

A transistor is a three terminal device. The terminals are emitter, base, collector. In common emitter configuration, input voltage is applied between base and emitter terminals and out put

| NAME OF THE EQUIPMENT | RANGE               | QUANTITY |

|-----------------------|---------------------|----------|

| Transistor            | (BC 547)            |          |

| R.P.S                 | (0-30V)             |          |

| Voltmeters            | (0-20V)             |          |

| Ammeters              | (0-500)μA, (0-50)mA |          |

| Resistors             | 1ΚΩ                 |          |

| Bread board           |                     |          |

| Connecting Wires      |                     |          |

is taken across the collector and emitter terminals.

Therefore the emitter terminal is common to both input and output.

The input characteristics resemble that of a forward biased diode curve. This is expected since the Base-Emitter junction of the transistor is forward biased. As compared to CB arrangement  $I_B$  increases less rapidly with  $V_{BE}$ . Therefore input resistance of CE circuit is higher than that of CB circuit.

The output characteristics are drawn between  $I_c$  and  $V_{CE}$  at constant  $I_{B.}$  the collector current varies with  $V_{CE}$  unto few volts only. After this the collector current becomes almost

constant, and independent of  $V_{CE}$ . The value of  $V_{CE}$  up to which the collector current changes with  $V_{CE}$  is known as Knee voltage. The transistor always operated in the region above Knee voltage,  $I_C$  is always constant and is approximately equal to  $I_B$ . The current amplification factor of CE configuration is given by  $\beta = \Delta I_C/\Delta I_B$

# **CIRCUIT DIAGRAM:**

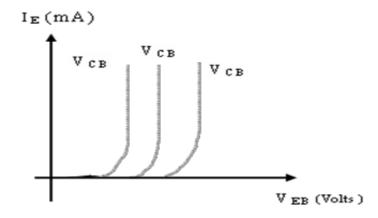

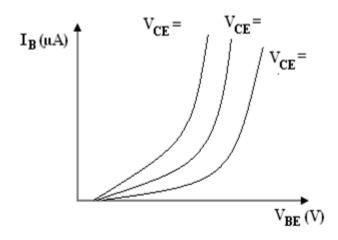

# **MODEL GRAPHS:**

# **INPUT CHARACTERSTICS:**

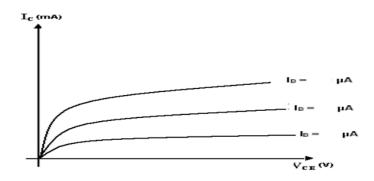

## **OUTPUT CHARECTERSTICS:**

# **PROCEDURE:**

#### **INPUT CHARECTERSTICS:**

- 1. Connect the circuit as per the circuit diagram.

- 2. For plotting the input characteristics the output voltage  $V_{CE}$  is kept constant at V and for different values of  $V_{BE}$ . Note down the values of  $I_{C}$

- 3. Repeat the above step by keeping  $V_{CE}$  at and  $V_{CE}$ .

- 4. Tabulate all the readings.

- 5. plot the graph between  $V_{BE}$  and  $I_B$  for constant  $V_{CE}$

# **OUTPUT CHARACTERSTICS:**

- 1. Connect the circuit as per the circuit diagram

- 2.for plotting the output characteristics the input current  $I_B$  is kept constant at  $\mu A$  and for different values of  $V_{CE}$  note down the values of  $I_C$

- 3.repeat the above step by keeping  $I_B$  at  $\mu A$

- 4.tabulate the all the readings

- 5.plot the graph between  $V_{CE}$  and  $I_{C}$  for constant  $I_{B}$

# **TABULAR COLUMNS:**

# **INPUT CHARACTERISTICS:**

| S.NO | V <sub>CE</sub> =   | V                   | $\mathbf{V}_{\mathrm{CE}} =$ | V                   | V <sub>CE</sub> =   | V                   |

|------|---------------------|---------------------|------------------------------|---------------------|---------------------|---------------------|

|      | V <sub>BE</sub> (V) | I <sub>B</sub> (µA) | V <sub>BE</sub> (V)          | I <sub>B</sub> (µA) | V <sub>BE</sub> (V) | I <sub>B</sub> (µA) |

|      |                     |                     |                              |                     |                     |                     |

|      |                     |                     |                              |                     |                     |                     |

|      |                     |                     |                              |                     |                     |                     |

|      |                     |                     |                              |                     |                     |                     |

# **OUTPUT CHAREACTARISTICS:**

| S.NO | $I_B = \mu$         | 4                   | $I_B =$             | μΑ                 | $I_B = \mu$         | A                   |

|------|---------------------|---------------------|---------------------|--------------------|---------------------|---------------------|

|      | V <sub>CE</sub> (V) | I <sub>C</sub> (mA) | V <sub>CE</sub> (V) | I <sub>C</sub> mA) | V <sub>CE</sub> (V) | I <sub>C</sub> (mA) |

|      |                     |                     |                     |                    |                     |                     |

|      |                     |                     |                     |                    |                     |                     |

|      |                     |                     |                     |                    |                     |                     |

|      |                     |                     |                     |                    |                     |                     |

# **PRECAUTIONS:**

- 1. The supply voltage should not exceed the rating of the transistor

- 2. Meters should be connected properly according to their polarities .

**RESULT:** Thus, studied the input and output characteristics of a transistor connected in common emitter configuration.

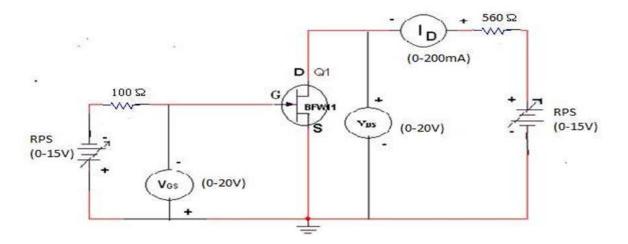

**OBJECTIVE:** To draw the drain and transfer characteristics of a given FET.

# **APPARATUS REQUIRED:**

JFET (BFW11)

Regulated Power Supply (0-15V)

Voltmeter (0-20V)

Ammeter (0-200mA)

Breadboard

Connecting wires

#### THEORY:

A FET is a three terminal device, having the characteristics of high input impedance and less noise, the Gate to Source junction of the FET s always reverse biased. In response to small applied voltage from drain to source, the n-type bar acts as sample resistor, and the drain current increases linearly with VDS. With increase in ID the ohmic voltage drop between the source and the channel region reverse biases the junction and the conducting position of the channel begins to remain constant. The VDS at this instant is called "pinch of voltage".

If the gate to source voltage (V<sub>GS</sub>) is applied in the direction to provide additional reverse bias, the pinch off voltage ill is decreased. In amplifier application, the FET is always used in the region beyond the pinch-off.

$$F_{DS} = I_{DSS}(1-V_{GS}/V_P)^2$$

#### **CIRCUIT DIAGRAM:**

#### **PROCEDURE:**

- 1. All the connections are made as per the circuit diagram.

- 2. To plot the drain characteristics, keep V<sub>GS</sub> constant at 0V.

- 3. Vary the V<sub>DD</sub> and observe the values of V<sub>DS</sub> and I<sub>D</sub>.

- 4. Repeat the above steps 2, 3 for different values of V<sub>GS</sub> at 0.1V and 0.2V.

- 5. All the readings are tabulated.

- 6. To plot the transfer characteristics, keep V<sub>DS</sub> constant at 1V.

- 7. Vary V<sub>GG</sub> and observe the values of V<sub>GS</sub> and I<sub>D</sub>.

- 8. Repeat steps 6 and 7 for different values of V<sub>DS</sub> at 1.5 V and 2V.

- 9. The readings are tabulated.

#### **OBSERVATIONS:**

# DRAIN CHARACTERISTICS:

| S.NO | VG                  | S=0V                | $V_{GS}$            | s=-1V               | $V_{GS}$            | s=-2V               |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) | V <sub>DS</sub> (V) | I <sub>D</sub> (mA) |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

#### TRANSFER CHARACTERISTICS:

| S.NO | $V_{\mathrm{DS}}$   | =0.5V               | $V_{DS}$            | S=1V                | V <sub>DS</sub>     | =1.5V               |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | V <sub>GS</sub> (V) | I <sub>D</sub> (mA) | V <sub>GS</sub> (V) | I <sub>D</sub> (mA) | V <sub>GS</sub> (V) | I <sub>D</sub> (mA) |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

|      |                     |                     |                     |                     |                     |                     |

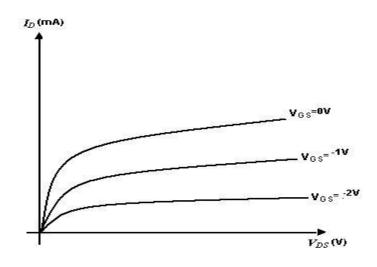

# **MODEL GRAPH**:

# DRAIN CHARACTERISTICS:

# TRANSFER CHARACTERISTICS:

**RESULT:** The drain and transfer characteristics of a FET are drawn.

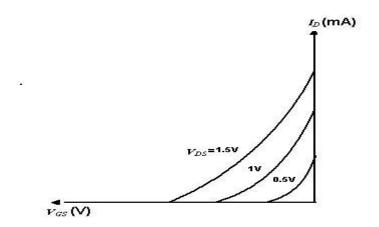

**OBJECTIVE:** To obtain characteristics of light emitting diode (LED)

APPARATUS REQUIRED

Led

Connecting Leads

Resistance

DC Supply

#### **Introduction:**

LED is semiconductor junction diode which emits light when current passes through it in forward bias condition. P type of semiconductor consists of large number of holes while N type of semiconductor consists of large number of electrons. At zero bias (no voltage across junction), depletion region exists and it separate out two regions. When LED is forward biased, barrier potential reduces and depletion region becomes narrow. Electron crosses the depletion region and recombines with holes. Similarly holes crosses depletion region and recombine with electrons. Each recombination of hole and electron produces photon (light) The intensity of light emitted depends on the number of minority carriers available for recombination. Wavelength (or frequency) of emitted light depends on band-gap energy. The light emitting diode works by the process of spontaneous emission.

Light source material must have direct band gap. In a direct band gap semiconductor material electron and hole recombine directly across band gap without need of third particle to conserve momentum.

Light source materials are made from compound of group-III (Al,Ga,In) and group-V (P,As,Sb) element. The wavelength generated by the LED depends on bandgap energy and bandgap energy depends on doping level of above elements. Let us understand relation between frequency of emission and energy.

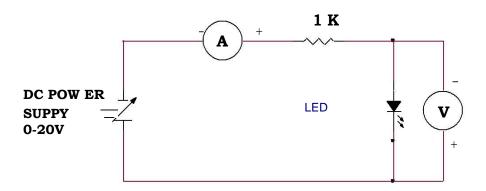

#### **Procedure:**

- 1. Connect the power supply, voltmeter, current meter with the LED as shown in the circuit diagram.

- 2. Increase voltage from the power supply from 0V to 20V in step as shown in the observation table

- 3. easure voltage across LED and current through the LED. Note down readings in the observation table and also observes light coming from LED.

- 4. Reverse DC power supply polarity for reverse bias

- 5. Repeat the above procedure for the different values of supply voltage for reverse bias

- 6. Draw VI characteristics for forward bias and reverse bias in one graph

# Circuit diagram (forward bias):

# Circuit diagram (reverse bias):

# FUNDAMENTALS OF ELECTRONICS ENGINEERING(BEC151/BEC251)

# **Observation table: (Forward bias)**

| Sr. No. | Supply voltage<br>(Volt) | Diode voltage<br>(Vd) | Diode current<br>(Id) |

|---------|--------------------------|-----------------------|-----------------------|

| 1.      | 0                        |                       |                       |

| 2.      | 0.5                      |                       |                       |

| 3.      | 1                        |                       |                       |

| 4.      | 2                        |                       |                       |

| 5.      | 5                        |                       |                       |

| 6.      | 10                       |                       |                       |

| 7.      | 15                       |                       |                       |

| 8.      | 20                       |                       |                       |

# **Observation table: (Reverse bias)**

| Sr. No. | Supply voltage | Diode voltage<br>(Vd) | Diode current<br>(Id) |

|---------|----------------|-----------------------|-----------------------|

| 1.      | 0              |                       |                       |

| 2.      | 2              |                       |                       |

| 3.      | 5              |                       |                       |

| 4.      | 10             |                       |                       |

| 5.      | 15             |                       |                       |

| 6.      | 20             |                       |                       |

Result: Thus studied the characteristics of LED and plotted the graph.

**OBJECTIVE:** Introduction to Digital Electronics Lab- Nomenclature of Digital Ics, Specifications, Study of the Data Sheet, Concept of  $V_{cc}$  and Ground, Verification of the Truth Tables of Logic Gates using TTL Ics.

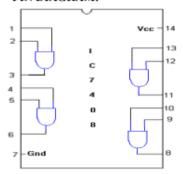

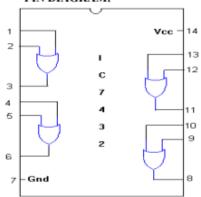

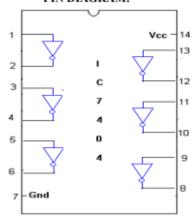

**APPARATUS REQUIRED:** Power Supply, Digital Trainer Kit., Connecting Leads,IC's (7400, 7402, 7404, 7408, 7432, and 7486)

#### **BRIEF THEORY:**

**AND Gate:** The AND operation is defined as the output as (1) one if and only if all the inputs are (1) one. 7408 is the two Inputs AND gate IC.A&B are the Input terminals &Yis the Output terminal.

$$Y = A.B$$

**OR Gate:** The OR operation is defined as the output as (1) one if one or more than 0 inputs are (1) one. 7432 is the two Input OR gate IC. A&B are the input terminals & Y is the Output terminal.

$$Y = A + B$$

**NOT GATE:** The NOT gate is also known as Inverter. It has one input (A) & one output (Y). IC No. is 7404. Its logical equation is,

$$Y = A NOT B, Y = A'$$

**NAND GATE:** The IC no. for NAND gate is 7400. The NOT-AND operation is known as NAND operation. If all inputs are 1 then output produced is 0. NAND gate is invertedAND gate.

$$Y = (A. B)$$

**NOR GATE:** The NOR gate has two or more input signals but only one output signal. IC7402 is two I/P IC. The NOT- OR operation is known as NOR operation. If all the inputs are 0 then the O/P is 1. NOR gate is inverted OR gate.

$$Y = (A+B)$$

**EX-OR GATE:** The EX-OR gate can have two or more inputs but produce one output. 7486 is two inputs IC. EX-OR gate is not a basic operation & can be performed using basic gates.

$$Y = A + B$$

# FUNDAMENTALS OF ELECTRONICS ENGINEERING(BEC151/BEC251)

# LOGIC SYMBOL:

#### SYMBOL:

TRUTH TABLE

| А | В | A.B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

OR GATE: SYMBOL:

TRUTH TABLE

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

NOT GATE: SYMBOL:

TRUTH TABLE:

| Α | Ā |  |

|---|---|--|

| 0 | 1 |  |

| 1 | 0 |  |

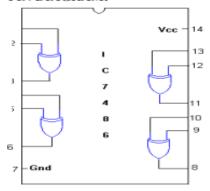

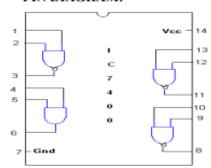

#### PIN DIAGRAM:

#### PIN DIAGRAM:

## PIN DIAGRAM:

# FUNDAMENTALS OF ELECTRONICS ENGINEERING(BEC151/BEC251)

# XOR GATE:

#### SYMBOL:

#### TRUTH TABLE :

| А | В | ĀB + AB |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

# 2-INPUT NAND GATE: SYMBOL:

#### TRUTH TABLE

| Α | В | A + B |

|---|---|-------|

| 0 | 0 | 1     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 0     |

#### NOR GATE: SYMBOL:

#### TRUTH TABLE

| Α | В | A+B |  |

|---|---|-----|--|

| 0 | 0 | 1   |  |

| 0 | 1 | 1   |  |

| 1 | 0 | 1   |  |

| 1 | 1 | 0   |  |

#### PIN DIAGRAM:

#### PIN DIAGRAM:

#### PIN DIAGRAM:

#### **PROCEDURE:**

- (a) Fix the IC's on breadboard & give the supply.

- (b) Connect the +ve terminal of supply to pin 14 & -ve to pin 7.

- (c) Give input at pin 1, 2 & take output from pin 3. It is same for all except NOT & NOR IC.

- (d) For NOR, pin 1 is output & pin 2&3 are inputs.

- (e) For NOT, pin 1 is input & pin 2 is output.

- (f) Note the values of output for different combination of inputs & draw the TRUTH TABLE.

#### **OBSERVATION TABLE:**

| INP | UTS |           |           |               | OUTPUTS      |                |                |

|-----|-----|-----------|-----------|---------------|--------------|----------------|----------------|

| A   | В   | A'<br>NOT | A+B<br>OR | (A+B)'<br>NOR | (A*B)<br>AND | (A*B)'<br>NAND | (A4B)<br>Ex-OR |

| 0   | 0   | 1         | 0         | 1             | 0            | 1              | 0              |

| 0   | 1   | 1         | 1         | 0             | 0            | 1              | 1              |

| 1   | 0   | 0         | 1         | 0             | 0            | 1              | 1              |

| 1   | 1   | 0         | 1         | 0             | 1            | 0              | 0              |

**RESULT:** We have learnt all the gates ICs according to the IC pin diagram.

#### **PRECAUTIONS:**

- 1. Make the connections according to the IC pin diagram.

- 2. The connections should be tight.

- 3. The V<sub>cc</sub> and ground should be applied carefully at the specified pin only.

This lab manual has been updated by

Dr.Kamal deep

(kamal.deep@gnindia.dronacharya.info)

Crosschecked ByHOD ECE

Please spare some time to provide your valuable feedback.