B-27, Knowledge Park – III, Greater Noida Uttar Pradesh - 201308 Approved by: All India Council for Technical Education (AICTE), New Delhi Affiliated to: Dr. A. P. J. Abdul Kalam Technical University (AKTU), Lucknow

# DEPARTMENT OF INFORMATION TECHNOLOGY

# **Computer Organization and Architecture**

# Lab Manual

**SUBJECT CODE: BCS-352**

# **B.Tech.**, Semester -III

Session: 2024-25, ODD Semester

# **Table of Contents**

- 1. Vision and Mission of the Institute.

- 2. Vision and Mission of the Department.

- 3. Program Outcomes (POs).

- 4. Program Educational Objectives and Program Specific Outcomes (PEOs and PSOs).

- 5. University Syllabus.

- 6. Course Outcomes (COs).

- 7. Course Overview.

- 8. List of Experiments mapped with COs.

- 9. DO's and DON'Ts.

- 10. General Safety Precautions.

- 11. Guidelines for students for report preparation.

- 12.Lab Experiments

# DRONACHARYA GROUP OF INSTITUTIONS GREATER NOIDA

#### VISION

• Instilling core human values and facilitating competence to address global challenges by providing Quality Technical Education.

## MISSION

- M1 Enhancing technical expertise through innovative research and education, fostering creativity and excellence in problem-solving.

- M2 Cultivating a culture of ethical innovation and user-focused design, ensuring technological progress enhances the well-being of society.

- M3 Equipping individuals with the technical skills and ethical values to lead and innovate responsibly in an ever-evolving digital land.

# **DEPARTMENT OF INFORMATION TECHNOLOGY**

## VISION

To provide students with theoretical understanding and technical proficiency in Information Technology, instill with moral and ethical values, to excel in academic, industry, and research settings.

## MISSION

M1: To instill in students a strong foundation of both the theory and practical application of IT skills, combined with the innovation and research approaches to keep pace with emerging technologies.

M2: To empower graduates to become global leaders specializing in field of Information Technology.

M3: To impart to students the social, ethical, and moral values necessary for them to make substantial contributions to society.

#### **Program Outcomes (POs)**

**PO1: Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

**PO2: Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**PO3: Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

**PO4: Conduct investigations of complex problems:** Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

**PO5: Modern tool usage:** Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

**PO6: The engineer and society:** Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

**PO7: Environment and sustainability:** Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

**PO8: Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of engineering practice.

**PO 9: Individual and teamwork:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

**PO10: Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

**PO11: Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply theseto one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

**PO12: Life-long learning:** Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# **Programme Educational Objectives (PEOs)**

**PEO1:** Apply the knowledge of mathematics, science and engineering fundamentals to identify and solve IT and engineering problems.

**PEO2:** Use various software tools and technologies to solve problems related to academia, industry and society.

**PEO3:** Work with ethical and moral values in the multi-disciplinary teams and can communicate effectively among team members with continuous learning.

## **Program Specific Outcomes (PSOs)**

**PSO1:** Ability to think logically and apply programming knowledge and practices in analyzing real world problems and provide solutions to meet the needs of society.

**PSO2:** Enhance the competence of technocrats to provide professional engineering solutions as per the industrial and societal needs.

**PSO3:** To cultivate and produce highly motivated engineers committed to lifelong learning, pursuing research, higher education, and embracing competitive challenges to excel in the future.

# **University Syllabus**

- 1. Implementing HALF ADDER, FULL ADDER using basic logic gates

- 2. Implementing Binary-to-Gray, Gray-to-Binary code conversions.

- 3. Implementing 3-8 line DECODER.

- 4. Implementing 4x1 and 8x1 MULTIPLEXERS.

- 5. Verify the excitation tables of various FLIP-FLOPS.

- 6. Design of an 8-bit Input/Output system with four8-bit Internal Registers.

- 7. Design of an 8-bit ARITHMETIC LOGIC UNIT.

- 8. Design the data path of a computer from its register transfer language description.

- 9. Design the control unit of a computer using either hard wiring or micro programming based on its register transfer language description.

- 10. Implement a simple instruction set computer with a control unit and a data path.

# **Course Outcomes(COs)**

Upon successful completion of the course, the students will be able to

- **C.1:** Design and verify combinational circuits (adder, code converter, decoder, multiplexer) using basic gates.

- C.2: Design and verify various flip-flops.

- C.3: Design I/O system and ALU.

- C.4: Demonstrate a simple instruction set computer.

# **CO-PO Mapping:**

|     | PO1 | PO2 | PO3 | PO4 | <b>PO5</b> | <b>PO6</b> | <b>PO7</b> | <b>PO8</b> | <b>PO9</b> | PO10 | PO11 | PO12 |

|-----|-----|-----|-----|-----|------------|------------|------------|------------|------------|------|------|------|

| C.1 | 3   |     | 3   |     |            |            |            | 2          | 2          | 2    |      | 2    |

| C.2 | 3   |     | 3   |     |            |            |            | 2          | 2          | 2    |      | 2    |

| C.3 | 3   |     | 3   |     |            |            |            | 2          | 2          | 2    |      | 2    |

| C.4 | 2   |     | 3   |     |            |            |            | 2          | 2          | 2    |      |      |

# **CO-PSO Mapping**

|        | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C207.1 | -    | 3    | -    |

| C207.2 | -    | 3    | -    |

| C207.3 | -    | 3    | -    |

| C207.4 | -    | 3    | -    |

| C207   | -    | 3    | -    |

# **Course Overview**

An important part of the undergraduate curriculum for IT students is coverage of computer organization. Typically, this is accomplished by both a lecture and lab course. The purpose of thelabcourseistohavethestudentsdeveloppracticaldesignskills.Ourcomputerorganization laboratory course starts with traditional logic gate design, then gradually incorporates control unit, up to the point where students are building a simple instruction set computer. The laboratory course is scheduled for a two-hour time slot. There are ten lab experiments.

During the first set of Experiments, students become familiar with basic digital hardware by constructing simple combinational circuits, and learning troubleshooting skills. During the secondsetofExperiments,studentsbecomefamiliarwitharithmeticlogicunitandcontrolunit. Finally, students apply their knowledge to the design a simple instruction set computer. Because students are constructing complete computer organization projects, the computer organization lab typically requires more effort than traditional laboratory courses.

# ListofExperimentsmappedwithCOs

| SLno. | ListofExperiments                                                                                                                       | Course  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

|       |                                                                                                                                         | Outcome |  |  |  |

| 1.    | Implementing HALF ADDER, FULL ADDER using basic logic gates                                                                             | CO.1    |  |  |  |

| 2.    | Implementing Binary-to-Gray, Gray-to-Binary code conversions.                                                                           | CO.1    |  |  |  |

| 3.    | Implementing 3-8 line DECODER.                                                                                                          | CO.1    |  |  |  |

| 4.    | Implementing 4x1 and 8x1 MULTIPLEXERS.                                                                                                  | CO.1    |  |  |  |

| 5.    | Verify the excitation tables of various FLIP-FLOPS.                                                                                     | CO.2    |  |  |  |

| 6.    | Design of an 8-bit Input/Output system with four8-bit Internal Registers.                                                               | CO.2    |  |  |  |

| 7.    | Design of an 8-bit ARITHMETIC LOGIC UNIT.                                                                                               | CO.3    |  |  |  |

| 8.    | Design the data path of a computer from its register transfer language description.                                                     | CO.4    |  |  |  |

| 9.    | Design the control unit of a computer using either hardwiring or micro programming based on its register transfer language description. | CO.4    |  |  |  |

| 10.   | Implement a simple instruction set computer with a control unit and a data path.                                                        | CO.4    |  |  |  |

# **Dos and DON'Ts**

#### Dos

- 1. Login-on with your user name and password.

- 2. Log off the Computer every time when you leave the Lab.

- 3. Arrange your chair properly when you are leaving the lab.

- 4. Put your bags in the designated area.

- 5. Ask permission to print.

#### **DON'Ts**

- 1. Do not share your user name and password.

- 2. Do not remove or disconnect cables or hardware parts.

- 3. Do not personalize the computer setting.

- 4. Do not run programs that continue to execute after you log off.

- 5. Do not download or install any programs, games or music on computer in Lab.

- 6. Personal Internet use chat room for Instant Messaging (IM) and Sites Strictly Prohibited.

- 7. No Internet gaming activities allowed.

- 8. Tea, Coffee, Water & Eatables are not allowed in the Computer Lab.

# **General Safety Precautions**

#### **Precaution (In case of Injury or Electric Shock)**

- 1. To break the victim with live electric source .Use an insulator such as fire wood or plastic to break the contact. Do not touch the victim with bare hands to avoid the risk of electrifying yourself.

- 2. Unplug the risk of faulty equipment. If main circuit breaker is accessible, turn the circuit off.

- 3. If the victim is unconscious, start resuscitation immediately, use your hands to press the chest in and out to continue breathing function. Use mouth-to-mouth resuscitation if necessary.

- 4. Immediately call medical emergency and security. Remember! Time is critical; be best.

#### **Precaution (In case of Fire)**

- 1. Turn the equipment off. If power switch is not immediately accessible, take plug off.

- 2. If fire continues, try to curb the fire if possible by using the fire extinguisher or by covering it with a heavy cloth if possible isolate the burning equipment from the other surrounding equipment.

- 3. Sound the fire alarm by activating the nearest alarm switch located in the hall way.

- 4. Call security and emergency department immediately:

# Guidelinestostudentsforreportpreparation

All students are required tomaintain a record of the experiments conducted bythem. Guidelines for its preparation are as follows: -

1) Allfilesmustcontainatitlepagefollowedbyanindexpage. *Thefileswillnotbesignedby the faculty without an entry in the index page*.

- 2) Student'sName,Rollnumberanddateofconductionofexperimentmustbewrittenonall pages.

- 3) Foreachexperiment, the record must contain the following

- (i) Aim/Objectiveoftheexperiment

- (ii) Equipment'srequired

- (iii) Pre-experimentwork(as givenbythefaculty)

- (iv) Observationtable

- (v) Results/output

#### Note:

- 1. Studentsmustbringtheirlabrecordalongwiththemwhenevertheycomeforthe lab.

- 2. Studentsmustensurethattheirlabrecordisregularlyevaluated.

# LabAssessmentCriteria

Anestimated10labclasses areconducted inasemesterfor eachlabcourse. Theselabclasses are assessed continuously. Each lab experiment is evaluated based on 5 assessment criteria as shown in following table. Assessed performance in each experiment is used to compute CO attainment as well as internal marks in the lab course.

| Grading<br>Criteria                                                                                 | Exemplary(4)                                                                                                                                                                             | Competent(3)                                                                                                                                     | Needs<br>Improvement<br>(2)                                                                                                                     | Poor(1)                                                                                                    |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| AC1:<br>Pre-Lab<br>written work<br>(for last lab<br>class, this may<br>be assessed<br>through viva) | Complete<br>procedure with<br>underlined<br>concept is<br>properly written                                                                                                               | Underlined<br>concept is<br>written but<br>procedure is<br>incomplete                                                                            | Notabletowrite<br>concept and<br>procedure                                                                                                      | Underlined<br>concept is not<br>clearly<br>understood                                                      |

| AC2:<br>Program<br>Writing/<br>Modeling                                                             | Assignedproblem<br>is<br>properlyanalyzed,<br>correct<br>solutiondesigned,<br>appropriate<br>language<br>constructs/ tools<br>are applied,<br>Program/solution<br>written is<br>readable | Assigned<br>problem is<br>properly<br>analyzed,<br>correctsolution<br>designed,<br>appropriate<br>language<br>constructs/tools<br>are<br>applied | Assigned<br>problem is<br>properly<br>analyzed<br>&<br>correct solution<br>designed                                                             | Assigned<br>problem is<br>properly<br>analyzed                                                             |

| AC3:<br>Identification<br>& Removalof<br>errors/ bugs                                               | Able to identify<br>errors/ bugs and<br>remove them                                                                                                                                      | Abletoidentify<br>errors/ bugsand<br>remove them<br>with little bit of<br>guidance                                                               | Is dependent<br>totally on<br>someone for<br>identification of<br>errors/ bugs and<br>their removal                                             | Unable to<br>understand the<br>reasonfor<br>errors/ bugs<br>evenafterthey<br>are explicitly<br>pointed out |

| <u>AC4:</u> Execution<br>&Demonstratio<br>n                                                         | All variants of<br>input/output are<br>tested,Solutionis<br>welldemonstrated<br>and implemented<br>concept is clearly<br>explained                                                       | Allvariantsof<br>input /output<br>are not tested,<br>However,<br>solution is well<br>demonstrated<br>and<br>implemented<br>concept is            | Only few<br>variantsofinput<br>/output are<br>tested,<br>Solutioniswell<br>demonstratedbut<br>implemented<br>concept is not<br>clearlyexplained | Solution isnot<br>well<br>demonstrated<br>and<br>implemented<br>concept is not<br>clearly<br>explained     |

|                                 |                                                                                                                                                                                     | clearly<br>explained                                                                                                                                                                                                      |                                                                                                                                                                                                                      | Leader 400/                                                                                                                                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC5:Lab<br>Record<br>Assessment | All assigned<br>problemsarewell<br>recorded with<br>objective,design<br>constructsand<br>solution along<br>with<br>Performance<br>analysisusingall<br>variantsofinput<br>and output | Morethan70%<br>of the assigned<br>problems are<br>well recorded<br>with objective,<br>designcontracts<br>and<br>solution along<br>with<br>Performance<br>analysisisdone<br>with all<br>variants of<br>input and<br>output | Lessthan70% of<br>the assigned<br>problems are<br>well recorded<br>with objective,<br>design contracts<br>and solution<br>along with<br>Performance<br>analysisisdone<br>with all variants<br>of input and<br>output | Lessthan40%<br>of the assigned<br>problems are<br>well recorded<br>with objective,<br>designcontracts<br>and<br>solution along<br>with<br>Performance<br>analysisisdone<br>with all<br>variants of<br>input and<br>output |

# LABEXPERIMENTS

# **LABEXPERIMENT1**

**OBJECTIVE**:DesignandimplementationofHalfAdderandFullAdder.

#### EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipment's         | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   |               | 1        |

| SL.No. | Components | Specification                      | Quantity |

|--------|------------|------------------------------------|----------|

| 1      | DigitalICs | 7400,7402,7404,<br>7408,7432,7486. | 1each    |

| 2      | Patchcords | -                                  | 6        |

#### **BRIEFDESCRIPTION:**

• Todesignandimplementhalfadderusinglogic gates

#### HALFADDER

| INPUTA | INPUTB | OUTPUTS |   |  |

|--------|--------|---------|---|--|

| INPUIA | INPUID | S       | С |  |

| 0      | 0      | 0       | 0 |  |

| 0      | 1      | 1       | 0 |  |

| 1      | 0      | 1       | 0 |  |

| 1      | 1      | 0       | 1 |  |

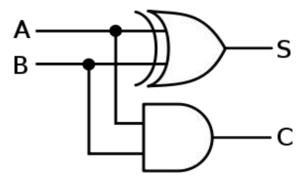

CircuitDiagram

TruthTable

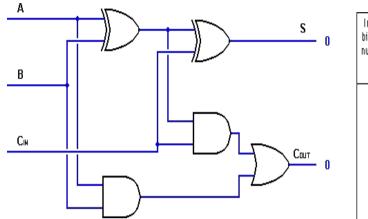

• Todesignandimplementfulladderusinglogic gates.

#### **FULLADDER**

| Input<br>bit for<br>number<br>B | Carry<br>bit<br>input<br>C <sub>IN</sub>             | Sum<br>bit<br>output<br>S                                                               | Carry<br>bit<br>output<br>C <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                               | 0                                                    | 0                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                               | 1                                                    | 1                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                               | 0                                                    | 1                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                               | 1                                                    | 0                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                               | 0                                                    | 1                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                               | 1                                                    | 0                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                               | 0                                                    | 0                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                               | 1                                                    | 1                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | bit for<br>number<br>B<br>0<br>0<br>1<br>1<br>1<br>0 | bit for<br>number<br>B C <sub>IN</sub><br>O 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>0 1 | bit for bit output output<br>B CIN S O 0 0 O 1 1 O 1 O 0 1 O 1 O 1 O 0 1 O 1 O 0 1 O 0 1 O 0 1 O 0 1 O 0 1 O 0 1 O 1 0 O 0 1 O 0 1 O 0 1 O 0 0 1 O 0 0 1 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 0 O 0 0 O 0 0 0 O 0 0 O 0 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O 0 0 O |

#### CIRCUITDIAGRAM

#### TRUTHTABLE

#### **PRE-EXPERIMENTQUESTIONS:-**

- 1. Explainthetruthtableofhalfadder.

- 2. HowmanyEx-orandor orgatecanbeusedtomakeahalfadder?

#### **PROCEDURE:-**

- Identifythepins.

- Connectthecircuitaspercircuitdiagram.

- Obtainoutputs with various input combinations.

- VerifyitwiththeBooleanfunctionusingtruthtable

#### **POST-EXPERIMENTQUESTIONS:-**

- 1. Whataretheapplicationsofhalfadder?

- 2. Whataretheapplicationoffulladder?

## **LABEXPERIMENT2**

$OBJECTIVE: Design and implementation of Binary to Gray, Gray to Binary Code \ conversions$

## EQUIPMENTS&COMPONENTSREQUIRED:

| SL.<br>No. | Equipments          | Specification | Quantity |

|------------|---------------------|---------------|----------|

| 1          | DigitalICTrainerkit | -             | 1        |

| 2          | DigitalMultimeter   |               | 1        |

| SL.<br>No. | Components | Specification                              | Quantity |  |

|------------|------------|--------------------------------------------|----------|--|

| 1          | DigitalICs | 7400,7402,<br>7404,<br>7408,7432,<br>7486. | 1each    |  |

| 2          | Patchcords | -                                          | 6        |  |

#### **BRIEFDESCRIPTION:**

$a) \ To design and implement Binary to Gray Code conversions$

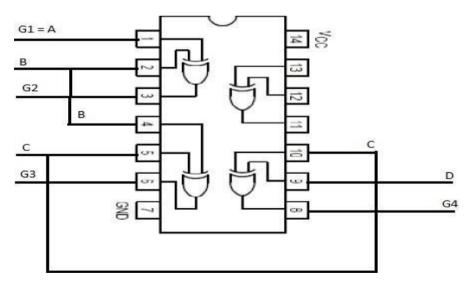

PindiagramofBinarytograycodeconverterusing7486IC(ex-or Gate)

| INI | INPUTS |   |   |    | OUTPUTS    |                |    |  |

|-----|--------|---|---|----|------------|----------------|----|--|

| Α   | B      | С | D | G4 | <b>G</b> 3 | G <sub>2</sub> | G1 |  |

| 0   | 0      | 0 | 0 | 0  | 0          | 0              | 0  |  |

| 0   | 0      | 0 | 1 | 0  | 0          | 0              | 1  |  |

| 0   | 0      | 1 | 0 | 0  | 0          | 1              | 1  |  |

| 0   | 0      | 1 | 1 | 0  | 0          | 1              | 0  |  |

| 0   | 1      | 0 | 0 | 0  | 1          | 1              | 0  |  |

| 0   | 1      | 0 | 1 | 0  | 1          | 1              | 1  |  |

| 0   | 1      | 1 | 0 | 0  | 1          | 0              | 1  |  |

| 0   | 1      | 1 | 1 | 0  | 1          | 0              | 0  |  |

| 1   | 0      | 0 | 0 | 1  | 1          | 0              | 0  |  |

| 1   | 0      | 0 | 1 | 1  | 1          | 0              | 1  |  |

| 1   | 0      | 1 | 0 | 1  | 1          | 1              | 1  |  |

| 1   | 0      | 1 | 1 | 1  | 1          | 1              | 0  |  |

| 1   | 1      | 0 | 0 | 1  | 0          | 1              | 0  |  |

| 1   | 1      | 0 | 1 | 1  | 0          | 1              | 1  |  |

| 1   | 1      | 1 | 0 | 1  | 0          | 0              | 1  |  |

| 1   | 1      | 1 | 1 | 1  | 0          | 0              | 0  |  |

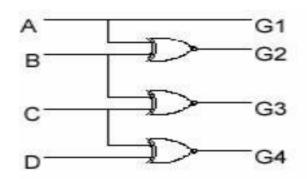

CircuitDiagramofBinarytoGrayCode Converter

TruthTable

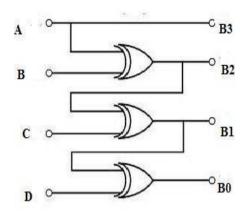

b) TodesignandimplementBinarytoGrayCodeconversions

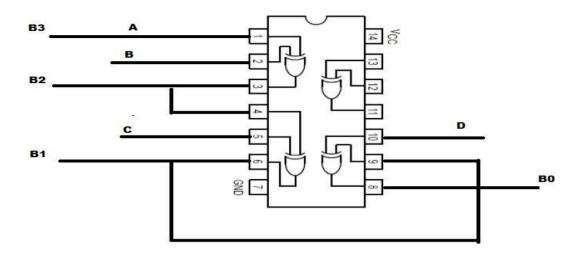

PindiagramofGraytoBinarycodeconverter using7486Ic(Exor Gate)

| INI | INPUTS |   |   | OUTPUTS    |            |            |    |

|-----|--------|---|---|------------|------------|------------|----|

| A   | B      | C | D | <b>B</b> 3 | <b>B</b> 2 | <b>B</b> 1 | Bo |

| 0   | 0      | 0 | 0 | 0          | 0          | 0          | 0  |

| 0   | 0      | 0 | 1 | 0          | 0          | 0          | 1  |

| 0   | 0      | 1 | 1 | 0          | 0          | 1          | 0  |

| 0   | 0      | 1 | 0 | 0          | 0          | 1          | 1  |

| 0   | 1      | 1 | 0 | 0          | 1          | 0          | 0  |

| 0   | 1      | 1 | 1 | 0          | 1          | 0          | 1  |

| 0   | 1      | 0 | 1 | 0          | 1          | 1          | 0  |

| 0   | 1      | 0 | 0 | 0          | 1          | 1          | 1  |

| 1   | 1      | 0 | 0 | 1          | 0          | 0          | 0  |

| 1   | 1      | 0 | 1 | 1          | 0          | 0          | 1  |

| 1   | 1      | 1 | 1 | 1          | 0          | 1          | 0  |

| 1   | 1      | 1 | 0 | 1          | 0          | 1          | 1  |

| 1   | 0      | 1 | 0 | 1          | 1          | 0          | 0  |

| 1   | 0      | 1 | 1 | 1          | 1          | 0          | 1  |

| 1   | 0      | 0 | 1 | 1          | 1          | 1          | 0  |

| 1   | 0      | 0 | 0 | 1          | 1          | 1          | 1  |

#### Circuit Diagram for Gray to Binary Code Converter

#### TRUTHTABLE

#### **PRE-EXPERIMENTQUESTIONS:-**

- 1 Whatisacodeconverter.

- 2 Differentiatebetweentranslatorandcodeconverter.

#### **PROCEDURE:-**

- Collectthecomponentsnecessarytoaccomplishthisexperiment.

- PlugtheICchipintothebreadboard.

- Connectthesupplyvoltageandgroundlinestothechips.PIN7=GroundandPIN14=+5V.

- Makeconnectionsasshownintherespectivecircuitdiagram.

- Connecttheinputsofthegatetotheinputswitches of the LED.

- ConnecttheoutputofthegatetotheoutputLEDs.

- Onceallconnectionshavebeendone,turnonthepowerswitchofthebreadboard

- Operate the switches and fill in the truth table (Write"1" if LED is ON and "0" if L1 is OFF Apply the various combination of inputs according to the truth table and observe the condition of Output LEDs.

## **POST-EXPERIMENTQUESTIONS:-**

- 1. Whataretheadvantagesofcodeconverter?

- 2. Whatarethepropertiesofgraycode?

## **LABEXPERIMENT3**

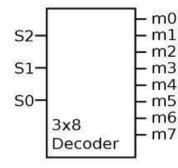

**OBJECTIVE:**Designandimplementationof2-4and3-8linedecoder.

#### EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipments          | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   |               | 1        |

| S | Components | Specification                              | Quantity |

|---|------------|--------------------------------------------|----------|

| 1 | DigitalICs | 7400,7402,<br>7404,<br>7408,7432,<br>7486. | 1each    |

| 2 | Patchcords | -                                          | 6        |

#### **BRIEFDESCRIPTION:**

**a)** 2to4Decoderusinglogicgates:

| $\overline{E}$ | $A_{\rm l}$ | $A_0$ | $\overline{D}_0$ | $\overline{D}_1$ | $\overline{D}_2$ | $\overline{D}_3$ |

|----------------|-------------|-------|------------------|------------------|------------------|------------------|

| 0              | 0           | 0     | 0                | 1                |                  | 1                |

| 0              | 0           | 1     | 1                | 0                | 1                | 1                |

| 0              | 1           | 0     | 1                | 1                | 0                | 1                |

| 0              | 1           | 1     | 1                | I                | 1                | 0                |

| 1              | Х           | Х     | 1                | 1                | 1                | 1                |

LogicDiagram

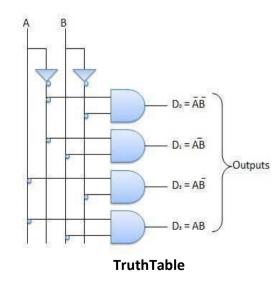

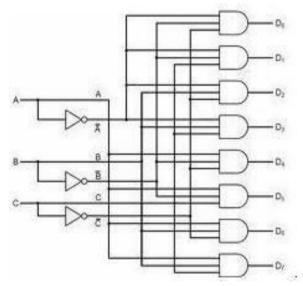

**b)** 3to8decoderusinglogic gates:

| Α. | В | C | DO | DI | D2 | D3 | D4 | D5 | D6 | D7 |

|----|---|---|----|----|----|----|----|----|----|----|

| 0  | 0 | 0 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 0 | 1 | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 1 | 0 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0  | 1 | 1 | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1  | 0 | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1  | 0 | 1 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1  | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1  | 1 | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

#### SYMBOL

#### LOGICDIAGRAMOF3T08DECODER:

#### **PRE-EXPERIMENTQUESTIONS:**

- 1. DifferencebetweenEncoderandDecoder.

- 2. Explaintheneedofmultiplexer.

#### **PROCEDURE**:

- Collectthecomponentsnecessarytoaccomplishthisexperiment.

- PlugtheICchipintothebreadboard.

- Connectthesupplyvoltage and ground linest othechips. PIN7=Ground

- and PIN14=+5V.

- Makeconnectionsasshownintherespectivecircuitdiagram.

- Connecttheinputsofthegatetotheinputswitches of the LED.

- ConnecttheoutputofthegatetotheoutputLEDs.

- Onceallconnectionshavebeendone,turnonthepowerswitchofthebreadboard

#### TRUTHTABLE

• Operate the switches and fill in the truth table (Write"1" if LED is ON and "0" if L1 is OFF Apply the various combination of inputs according to the truth tab alend observe the condition of Output LEDs.

## **POSTEXPERIMENTQUESTIONS:**

- 1. Designa5to32decoderusingone2to4and four3 to8decoderic's.

- 2. Writeanoteon BCDtodecimal decoder.

## **LABEXPERIMENT4**

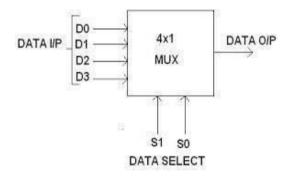

## OBJECTIVE: Implementation Of 4x1 And 8x1 Multiplxer

#### EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipment's         | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   |               | 1        |

| SL.No. | Components | Specification                              | Quantity |

|--------|------------|--------------------------------------------|----------|

| 1      | DigitalICs | 7400,7402,<br>7404,<br>7408,7432,<br>7486. | 1each    |

| 2      | Patchcords | -                                          | 6        |

#### **BRIEFDESCRIPTION:**

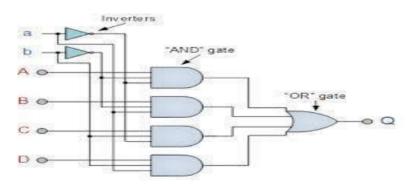

#### a)4to1MULTIPLEXERS:

| Addre | essing | Input<br>Selected |

|-------|--------|-------------------|

| b     | а      | Selected          |

| 0     | 0      | А                 |

| 0     | 1      | В                 |

| 1     | 0      | С                 |

| 1     | 1      | D                 |

#### LOGICDIAGRAM:

#### **TRUTHTABLE:**

$Q = \bar{a}\bar{b}A + \bar{a}bB + a\bar{b}C + abD$

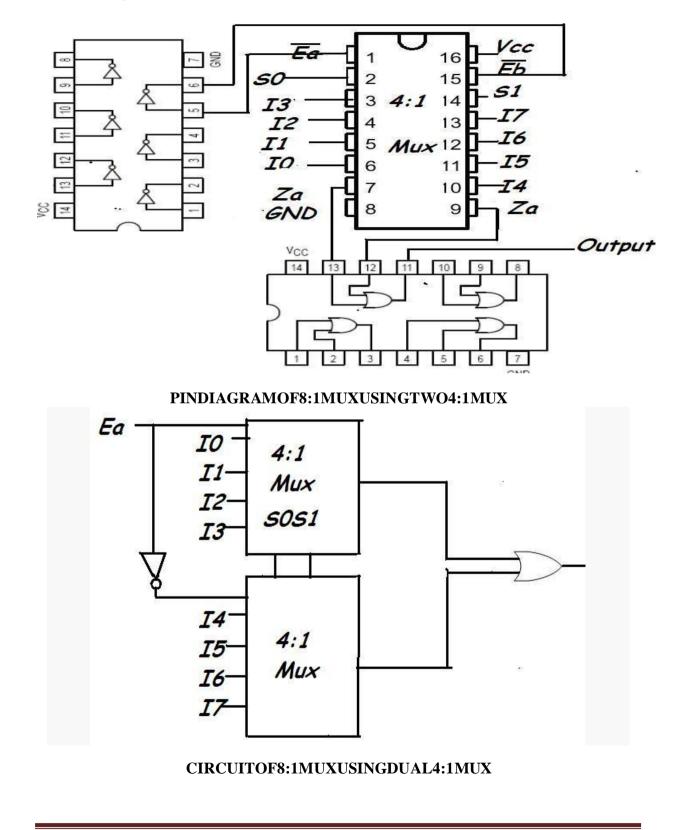

#### d) 8x1Multiplexer

| Sel | ectLin         | ies   |    |                |       | Inp            | outs |       |                |       | (  | Outpu | t |

|-----|----------------|-------|----|----------------|-------|----------------|------|-------|----------------|-------|----|-------|---|

| Ea  | S <sub>0</sub> | $S_1$ | Io | $\mathbf{I}_1$ | $I_2$ | I <sub>3</sub> | I4   | $I_5$ | I <sub>6</sub> | $I_7$ | Za | Zb    | Y |

| 0   | 0              | 0     | 0  | ×              | ×     | ×              | ×    | ×     | ×              | ×     | 0  | ×     | 0 |

| 0   | 0              | 0     | 1  | ×              | ×     | ×              | ×    | ×     | ×              | ×     | 1  | ×     | 1 |

| 0   | 0              | 1     | ×  | 0              | ×     | ×              | ×    | ×     | ×              | ×     | 0  | ×     | 0 |

| 0   | 0              | 1     | ×  | 1              | ×     | ×              | ×    | ×     | ×              | ×     | 1  | ×     | 1 |

| 0   | 1              | 0     | ×  | ×              | 0     | ×              | ×    | ×     | ×              | ×     | 0  | ×     | 0 |

| 0   | 1              | 0     | ×  | ×              | 1     | ×              | ×    | ×     | ×              | ×     | 1  | ×     | 1 |

| 0   | 1              | 1     | ×  | ×              | ×     | 0              | ×    | ×     | ×              | ×     | 0  | ×     | 0 |

| 0   | 1              | 1     | ×  | ×              | ×     | 1              | ×    | ×     | ×              | ×     | 1  | ×     | 1 |

| 1   | 0              | 0     |    | ×              | ×     | ×              | 0    | ×     | ×              | ×     | ×  | 0     | 0 |

| 1   | 0              | 0     | ×  | ×              | ×     | ×              | 1    | ×     | ×              | ×     | ×  | 1     | 1 |

| 1   | 0              | 1     | ×  | ×              | ×     | ×              | ×    | 0     | ×              | ×     | ×  | 0     | 0 |

| 1   | 0              | 1     | ×  | ×              | ×     | ×              | ×    | 1     | ×              | ×     | ×  | 1     | 1 |

| 1   | 1              | 0     | ×  | ×              | ×     | ×              | ×    | ×     | 0              | ×     | ×  | 0     | 0 |

| 1   | 1              | 0     | ×  | ×              | ×     | ×              | ×    | ×     | 1              | ×     | ×  | 1     | 1 |

| 1   | 1              | 1     | ×  | ×              | ×     | ×              | ×    | ×     | ×              | 0     | ×  | 0     | 0 |

| 1   | 1              | 1     | ×  | ×              | ×     | ×              | ×    | ×     | ×              | 1     | ×  | 1     | 1 |

#### TRUTHTABLEOF8:1MUXUSINGDUAL4:1MUX PRE

#### **EXPERIMENT QUESTIONS:-**

- 1. DifferencebetweenEncoderandDecoder.

- 2. Explaintheneedofmultiplexer.

#### **PROCEDURE:**-

- Collectthecomponentsnecessarytoaccomplishthisexperiment.

- PlugtheICchipintothebreadboard.

- Connectthesupplyvoltageandgroundlinestothechips.PIN7=Ground and PIN14 = +5V.

- Makeconnectionsasshownintherespectivecircuitdiagram.

- Connecttheinputsofthegatetotheinputswitches of the LED.

- ConnecttheoutputofthegatetotheoutputLEDs.

- Onceallconnectionshavebeendone,turnonthepowerswitchofthebreadboard

- Operatetheswitchesandfillinthetruthtable(Write"1"ifLEDisONand"0"ifL1 is OFF Apply the various combination of inputs according to the truth table and observe the condition of Output LEDs.

#### **POSTEXPERIMENTQUESTION:-**

1. Designa16 to1 Multiplexerusingone4to1MuxIC'S.

#### LABEXPERIMENT5

**OBJECTIVE:**VerifytheexcitationtablesofvariousFLIP-FLOPS.

#### EQUIPMENTS&COMPONENTSREQUIRED:

DigitalICtrainerkit,IC7400,IC7410,IC7473,IC7474,IC 7476

#### **BRIEFDESCRIPTION:**

Flipflopsarethebasicbuildingblocksinanymemorysystemssinceitsoutputwill remain in its state until it is forced to change it by some means.

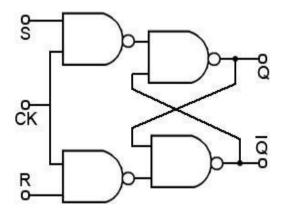

#### **SRFLIP FLOP:**

SandRstandsforsetandreset. There are four input combination possible at the inputs. But = = 1 is forbidden since the output will be indeterminate.

| 8        | INPUTS |      | OUTPU        | STATE         |

|----------|--------|------|--------------|---------------|

|          | 25.0   | 5051 | T            |               |

| CLK      | S      | R    | Q            | - X           |

| Х        | 0      | 0    | No<br>Change | Previous      |

| <b></b>  | 0      | 1    | 0            | Reset         |

| <b>♦</b> | 1      | 0    | 1            | Set           |

| ŕ        | 1      | 1    | -            | Forbidde<br>n |

#### LOGIC DIAGRAM OF R S FLIP FLOPS:

#### **TRUTHTABLE:**

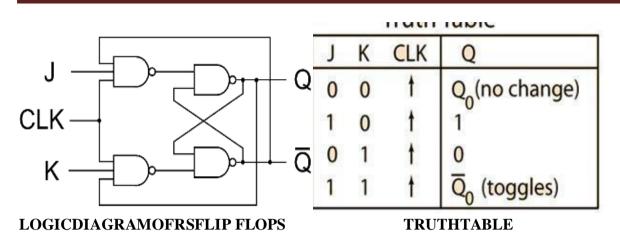

#### J K FLIP FLOP

TheindeterminateoutputstateofSRFFwhenS=R=1isavoidedbyconvertingittoaJKFF. When flip flop is switched on its output state is uncertain. When an initial state is to be assigned two separate inputs called preset and clear are used. They are active low inputs

ComputerOrganizationandArchitectureLab(BCS-352)

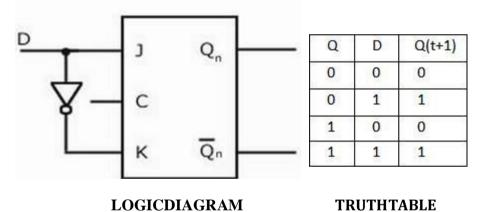

#### DFlipflop

It has only one input called as D input or Data input. The input data is transferred to the outputafteraclockisapplied.DFFcanbederivedfromJKFFbyusingJinputasDinput and J is inverted and fed to K input.

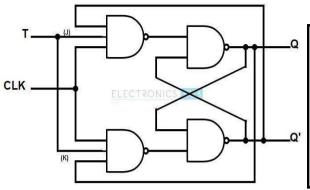

## TFlipFlop

TstandsforToggle.Theoutputtoggleswhenaclockpulseisapplied.TFFcanbederived from JK FF by shorting J and K input.

| T | $Q_n$ | $Q_{n+1}$ |

|---|-------|-----------|

| 0 | 0     | 0         |

| 0 | 1     | 1         |

| 1 | 0     | 1         |

| 1 | 1     | 0         |

#### T FLIP FLOP LOGIC DIAGRAM

#### TRUTHTABLE

#### **PRE-EXPERIMENT QUESTIONS:-**

**1.** Whatispropagationdelaytime?

2. HowisJKFFmadeto toggle?

#### **PROCEDURE:-**

- TestallcomponentsandICpackagesusingdigital ICtesterand multimeter

- SetupFFusingGatesandverifytheirtruthtables

- VerifytheTruthtablesof 7473,7474,and7476ICs

#### **POST-EXPERIMENTQUESTIONS:-**

**1.** HowmanyFFarein7475IC?

2. HowmanyFFarerequiredtoproduceadivide-by-128device?

#### **LABEXPERIMENT6**

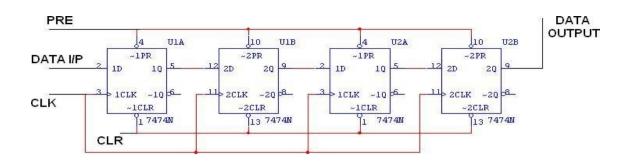

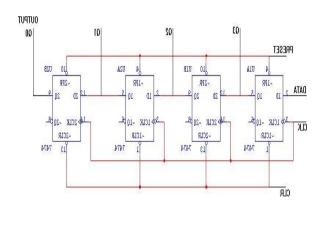

**OBJECTIVE:**DesignAndImplementationOfShiftRegisters(SISO&SIPO)

#### EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipments          | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   | -             | 1        |

| SL.No. | COMPONENT    | SPECIFICATION | QTY. |

|--------|--------------|---------------|------|

| 1.     | DFLIPFLOP    | IC7474        | 2    |

| 2.     | ICTRAINERKIT | -             | 1    |

| 3.     | PATCHCORDS   | _             | 15   |

#### **BRIEFDESCRIPTION:**

Aregisteriscapableofshiftingitsbinaryinformationinoneorbothdirectionsisknown as shift register. The logical configuration of shift register consist of a D-Flip flop cascaded with output of one flip flop connected to input of next flip flop. All flip flops receive common clock pulses which causes the shift in the output of the flip flop. The simplest possible shift register is one that uses only flip flop. The output of a given flip flopisconnected totheinputofnextflipflopoftheregister. Each clockpulseshiftsthe content of register one bit position to right.

(a) SerialinserialoutShiftRegister

(b) SerialinparalleloutShiftRegister

|      | 0   |   | 1         |

|------|-----|---|-----------|

| CLR0 | _ 1 | 1 | 14 — VCC  |

| D0   | - 2 | С | 13 — CLR1 |

| CLK0 | _ 3 | 7 | 12 — D1   |

| PRE0 | - 4 | 4 | 11 — CLK1 |

| S0   | _ 5 | 7 | 10 - PRE1 |

| s0   | _ 6 | 4 | 9 — Q1    |

| GND  | - 7 |   | 8 — Q1    |

|      |     |   |           |

#### PINDIAGRAM

#### LOGICDIAGRAM:SERIALINSERIALOUT

|     | Serialin | Serialout |

|-----|----------|-----------|

| CLK |          |           |

| 1   | 1        | 0         |

| 2   | 0        | 0         |

| 3   | 0        | 0         |

| 4   | 1        | 1         |

| 5   | X        | 0         |

| 6   | X        | 0         |

| 7   | X        | 1         |

#### TRUTHTABLE

#### SERIALINPARALLELOUT

LOGICDIAGRAM

|     |      | OUTPUT |    |    |   |  |  |

|-----|------|--------|----|----|---|--|--|

| CLK | DATA | QA     | QB | Qc | Q |  |  |

|     |      |        |    |    | D |  |  |

| 1   | 1    | 1      | 0  | 0  | 0 |  |  |

| 2   | 0    | 0      | 1  | 0  | 0 |  |  |

| 3   | 0    | 0      | 0  | 1  | 1 |  |  |

| 4   | 1    | 1      | 0  | 0  | 1 |  |  |

|     |      |        |    |    |   |  |  |

TRUTHTABLE

#### **PRE-EXPERIMENTQUESTIONS:-**

- 1. StatethefeaturesofIC7495.

- 2. StatethefeaturesofIC74195.

#### **PROCEDURE:-**

- Connectionsaregivenaspercircuitdiagram.

- Logicalinputsaregivenaspercircuitdiagram.

- Observetheoutputandverifythetruthtable.

#### **POST-EXPERIMENTQUESTIONS:-**

- 1. Howcanweuseshiftregistersinserialcommunications?Explain.

- 2. ListtheICswhichareusedas8bitSISO,SIPO,PISO,PIPOmodesandasa bidirectional shift register.

# **LABEXPERIMENT:7**

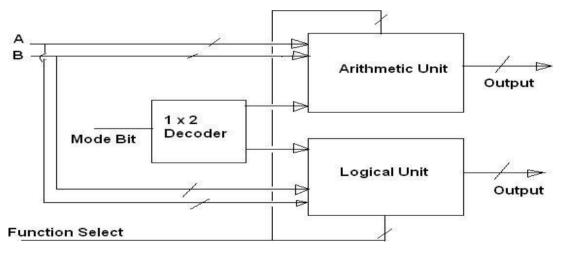

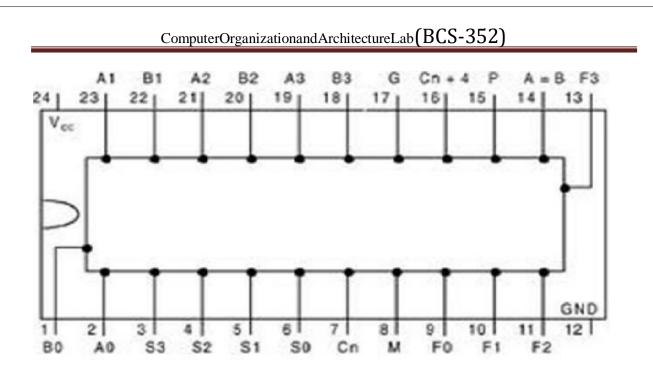

**OBJECTIVE:**Designandimplementationofan8bitarithmeticlogic unit.

### EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipments          | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   |               | 1        |

| SL.No. | COMPONENT  | SPECIFICATION | QTY. |

|--------|------------|---------------|------|

| 1.     | ALUIC      | IC7474        | 2    |

| 2.     | PATCHCORDS | -             | 15   |

#### **BRIEFDESCRIPTION:**

ALUstandsforthearithmeticandlogicalunitandisoneoftheimportantunitinalmostall the calculating machine these days be it with the hand-held mobile, or computers. All the computational work in the system are carried out by this unit. The typical ALU sizes are : 4-bit ALU : ALU that processes two 4-bit numbers.

8-bitALU:ALUthatprocessestwo8-bitnumbers.

StillinthelatestsystemsALUsizesare16,32,64-bitetc.Figure-1showstheblockdiagram of a typical ALU.

## **BlockDiagramofALU:**

In figure-1,the1x2selectorontheleftisasamodeselectortoselectoneofthetwounitsi.e. either the arithmetic unit or the logical unit. The function select lines are then used to select one of the many functions of arithmetic or the logical type.

MSIpackageforALU:-IC74181a4-bitArithmeticandlogicalunit:

PINDIAGRAMOFIC74181ALU

# SN54/74LS181

| М          | ODE S          | SELEC<br>UTS   | T  | 22-03-03-03-03-03-03-03-03-03-03-03-03-03- | VE LOW INPUTS<br>& OUTPUTS                        | SN-5723/3630     | VE HIGH INPUTS                               |

|------------|----------------|----------------|----|--------------------------------------------|---------------------------------------------------|------------------|----------------------------------------------|

| <b>S</b> 3 | S <sub>2</sub> | S <sub>1</sub> | So | LOGIC<br>(M = H)                           | ARITHMETIC <sup>**</sup><br>(M = L) ( $C_n = L$ ) | LOGIC<br>(M = H) | ARITHMETIC**<br>(M = L) (C <sub>n</sub> = H) |

| L          | L              | L              | L  | Ā                                          | A minus 1                                         | Ā                | A                                            |

| L          | L              | L              | н  | AB                                         | AB minus 1                                        | <u>A</u> + B     | A + <u>B</u>                                 |

| L          | L              | н              | L  | A + B                                      | AB minus 1                                        | AB               | A + B                                        |

| L          | L              | н              | Н  | Logical 1 r                                | ninus 1                                           | Logical 0 n      | ninus 1                                      |

| L          | н              | L              | L  | A + B                                      | A plus (A + B)                                    | AB               | A plus AB                                    |

| L          | н              | L              | н  | В                                          | AB plus (A + B)                                   | В                | (A + B) plus AB                              |

| L          | н              | н              | L  | A   B                                      | A minus B minus 1                                 | A ⊕ B            | A minus B minus 1                            |

| L          | н              | н              | Н  | A + B                                      | A + B                                             | AB               | AB minus 1                                   |

| Н          | L              | L              | L  | AB                                         | A plus (A + B)                                    | A + B            | A plus AB                                    |

| Н          | L              | L              | Н  | A   B                                      | A plus B                                          | A ⊕ B            | A plus B                                     |

| Н          | L              | Н              | L  | В                                          | AB plus (A + B)                                   | в                | (A + B) plus AB                              |

| н          | L              | Н              | Н  | A + B                                      | A + B                                             | AB               | AB minus 1                                   |

| н          | Н              | L              | L  | Logical 0 A                                | A plus A*                                         | Logical 1 A      | v plus A*                                    |

| н          | н              | L              | Н  | AB                                         | AB plus A                                         | A+B              | (A + B) plus A                               |

| Н          | Н              | н              | L  | AB                                         | AB plus A                                         | A + B            | (A + B) Plus A                               |

| н          | н              | н              | н  | A                                          | A                                                 | A                | A minus 1                                    |

#### FUNCTION TABLE

L = LOW Voltage Level

H = HIGH Voltage Level

\*Each bit is shifted to the next more significant position

\*\*Arithmetic operations expressed in 2s complement notation

#### **PRE-EXPEIMENTQUESTIONS:-**

**1.** WhatisDigitizing?

## **PROCEDURE:-**

- KeepthedatasheetofIC74181ready.

- InserttheIContheBreadboard.

- Makeconnectionsasshowninfigure.

- Verifytheconnections

# **POST-EXPEIMENTQUESTIONS:-**

1. Which Boolean operator combiness earch terms so that each search result contains all term?

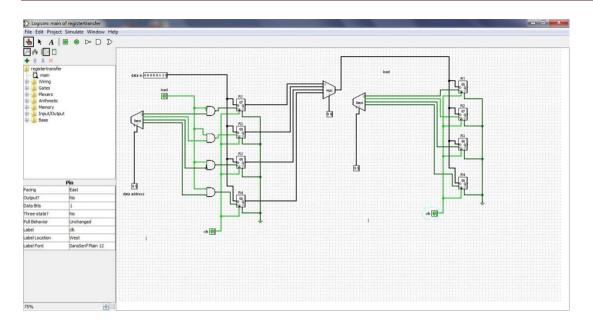

# LABEXPERIMENT8

**OBJECTIVE**: Design a data path of a computer from its register transfer language description.

## EQUIPMENTS&COMPONENTSREQUIRED:

| SL.No. | Equipment's         | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 1      | DigitalICTrainerkit | -             | 1        |

| 2      | DigitalMultimeter   |               | 1        |

| SL.No. | Components | Specification                      | Quantity |

|--------|------------|------------------------------------|----------|

| 1      | DigitalICs | 7400,7402,7404,<br>7408,7432,7486. | 1each    |

| 2      | Patchcords | -                                  | 6        |

#### **BRIEFDESCRIPTION:**

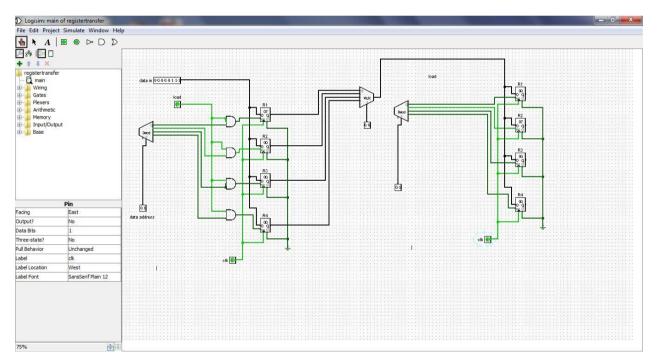

Thesymbolic notation used to describe them icro-operation transfers among registers is called Register Transfer Language. The term "register transfer" implies the availability of hardware logic circuits that can perform a stated micro-operation and transfer the result of the operation to the same or another register.

Astatementthatspecifiesaregistertransferimpliesthatcircuitsareavailablefrom the outputs of the source register to the inputs of the destination register and that the destination register has a parallel load capacity. If the transfer is to occur under a predetermined condition i.e.

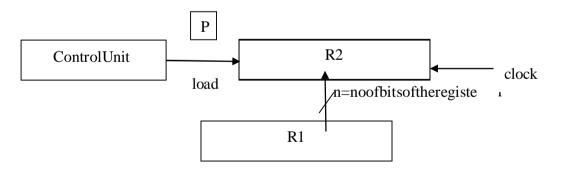

### If(P=1)thenR2 $\leftarrow$ R1

WherePisthecontrolsignal generated in the control section. A Control Function is a Boolean variable that is equal to 0 or 1

P:R2←R1

## **PRE-EXPERIMENTQUESTIONS:-**

- 1. Whatisthesignificance of DataPath?

- 2. WhatisRegisterTransfer Logic?

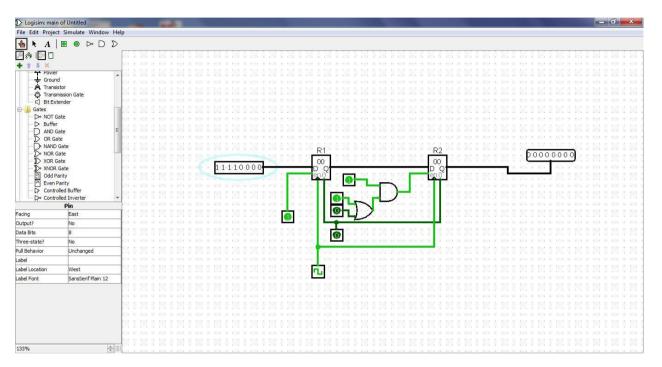

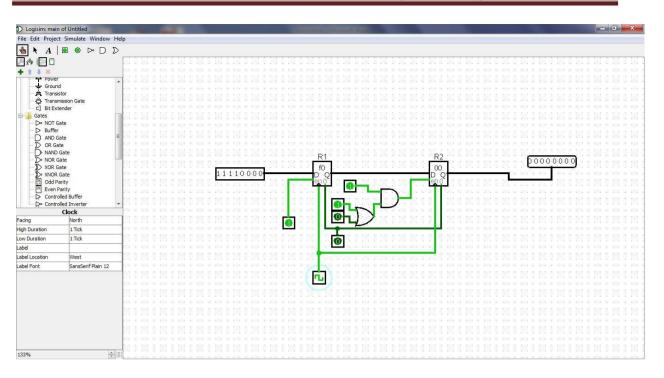

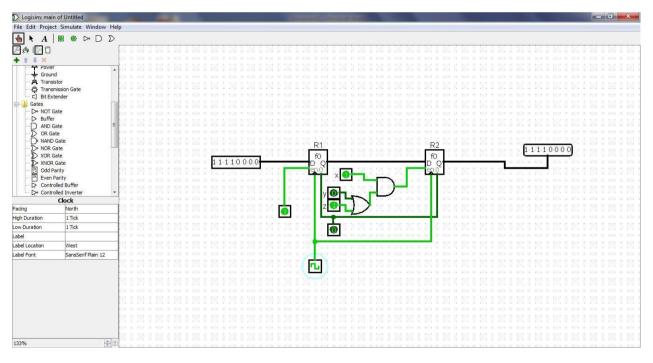

## **PROCEDURE:**-

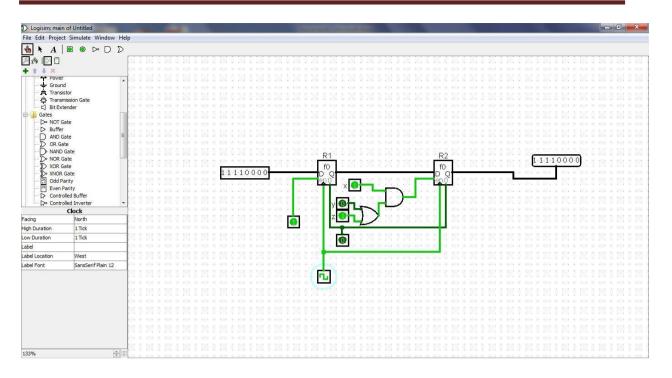

DatabitsReadytobetransferred

InthefirstclocktickRegisterR1storesthevalue

In the next clock pulse the value gets transferred to register R2 if its Enable input is high, i.e. its control function x.(y+z) = 1

RegisterTransferusingBUS

# **POST-EXPERIMENTQUESTIONS:-**

- 1. Howadatapathisdesigned?

- 2. Designadatapath for  $R_3 \leftarrow R_2 + R_1$

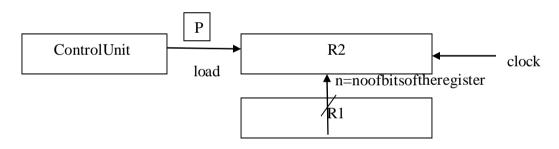

# **LABEXPERIMENT9**

OBJECTIVE: Designadata pathof a computer from its register transfer language description.

## EQUIPMENTS&COMPONENTSREQUIRED:

Registers ANDGates OR Gate ConnectingWires

# **BREIFDESCRIPTION:**

Thesymbolic notation used to describe them icro-operation transfers a mongregisters is called Register Transfer Language.

The term ``register transfer'` implies the availability of hardware logic circuits that can perform a stated micro-operation and transfer the result of the operation to the same or another register.

Astatementthatspecifiesaregistertransferimpliesthatcircuitsareavailablefrom the outputs of the source register to the inputs of the destination register and that the destination register has a parallel load capacity.

If the transfer is to occur under a predetermined condition i.e

If (P=1) then  $R2 \leftarrow R1$

WherePisthecontrolsignal generated in the control section. A Control Function is a Boolean variable that is equal to 0 or 1

```

P:R2←R1

```

# BLOCKDIAGRAM

# **PRE-EXPERIMENTQUESTIONS:-**

- 1. WhatisRTL?

- 2. Whatistheminimumno.ofregistersneededintheinstructionsetarchitectureofthe processor to compile a code with 3 operands?

# **PROCEDURE:**-

DatabitsReadytobetransfered

#### In the first clock tick Register R1 stores the value

In the next clock pulse the value get stransferred to register R2 if its Enable input is high, i.e. its control function x.(y+z) = 1

REGISTERTRANSFERUSINGBUS

# POST-EXPERIMENTQUESTION:-

1. WhatistheamountofROMneededtoimplementa4bitmultiplier.

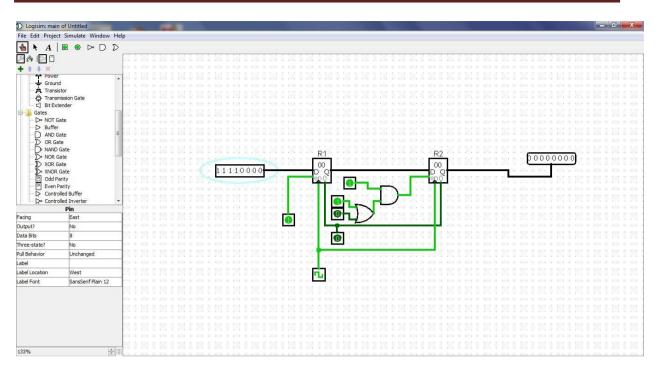

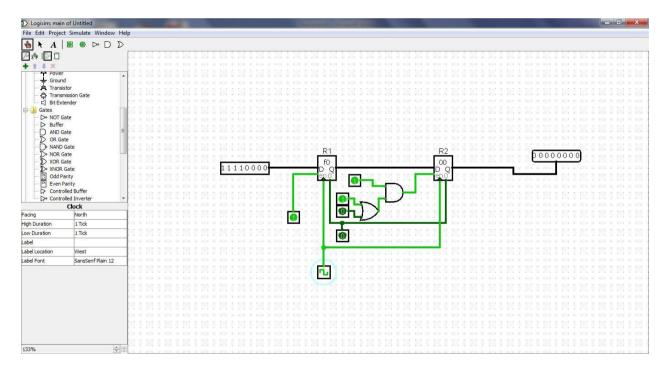

# LABEXPERIMENT10

**OBJECTIVE:**Design the control unit of a computer using hardwired based on its registertransfer language description.

#### **COMPONENTSREQUIRED:**

- 1.Registers

- 2. ANDGates

- 3. ORGate

- 4. Memory

- 5. DecodersandMultiplexers

- 6. ConnectingWires, etc.

#### **BREIFDESCRIPTION:**

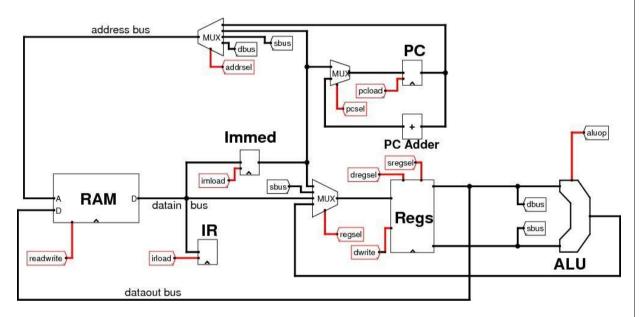

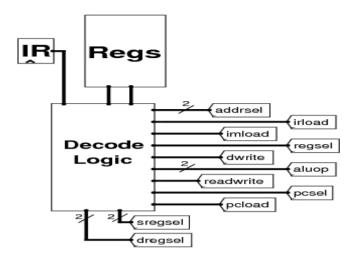

The controlunit (CU) is a component of a computer's central processing unit (CPU) that directs the operation of the processor. It tells the computer's memory, arithmetic/logic unit and input and output devices on how to respond to a program's instructions.

It directs the operation of the other units by providing timing and control signals. Most computer resources are managed by the CU. It directs the flow of data between the CPU and theotherdevices.TheControlUnit(CU)isdigitalcircuitrycontainedwithintheprocessorthat coordinatesthesequence of data movements into, out of, and between a processor's many sub- units. The result of these routed data movements through various digital circuits (sub-units) within the processor produces the manipulated data expected by a software instruction (loaded earlier, likely from memory). It controls (conducts) data flow inside the processor and additionally provides several external controls ignals to the result of the processor external destination's (i.e. memory).

## PRE-EXPERIMENTQUESTION:-

1. Why is register renaming done in pipelined processor.

## **PROCEDURE:-**

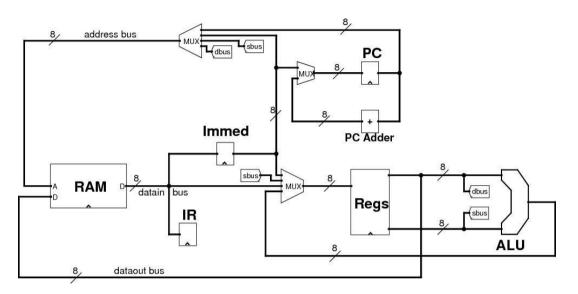

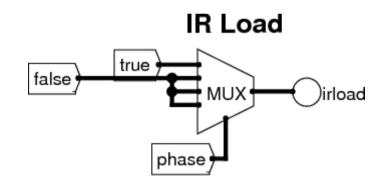

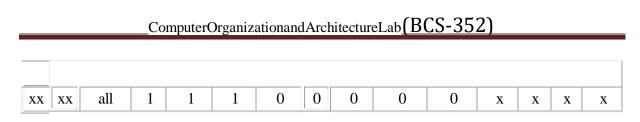

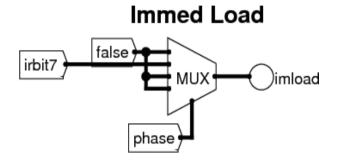

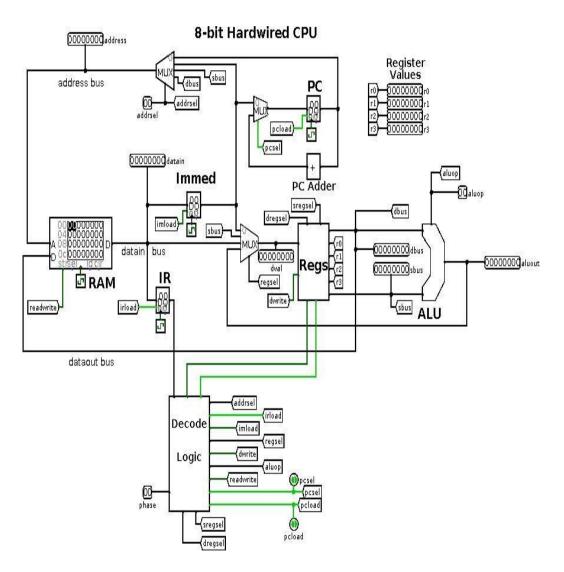

The CPU has an 8-bit data bus and an 8-bit address bus, so it can only support 256 by tes of memory to hold both instructions and data.

- Internally,therearefour8-bitregisters,R0toR3,plusanInstructionRegister,the Program Counter, and an 8-bit register which holds immediate values.

- TheALU is the same one that we designed last week. It performs the four operations AND, OR, ADD and SUB on two 8-bit values, and supports signed ADD sand SUBs.

- TheCPUisaload/storearchitecture:datahastobebroughtintoregistersfor manipulation, as the ALU only reads from and writes back to the registers.

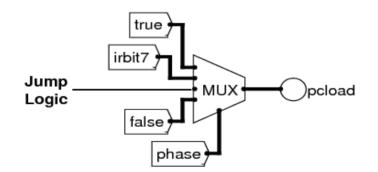

- TheALUoperationshavetwooperands:oneregisterisasourceregister,andthe second register is both source and destination register, i.e. destination register = destination register OP source register.